## **Analog Electronics**

### UNIT-I

### SINGLE STAGE AND MULTISTAGE AMPLIFIERS

### 1) Amplifier:

A amplifier is a circuit which increases the strength or weak signal.

### 2) CLASSIFICATION OF AMPLIFIER

### 1) CLASSIFICATION BASED ON FREQUENCY.

- 1) DC amplifier

- 2) audio amplifier (20 hz to 20khz)

- 3) video amplifier (few mhz)

- 4) radio frequency amplifier (khz to 20 mhz)

- 5) ultra high frequency (GHZ)

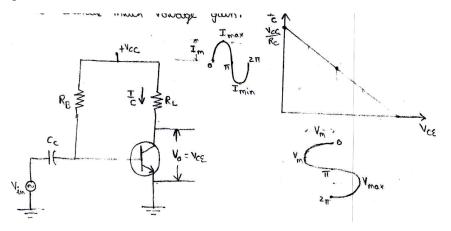

- 2) CLASSIFICATION BASED ON OPERATION.

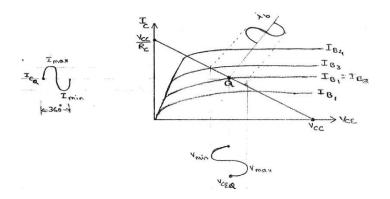

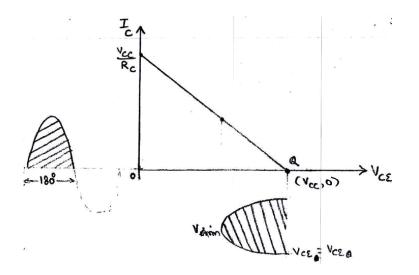

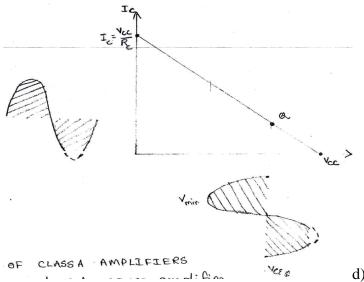

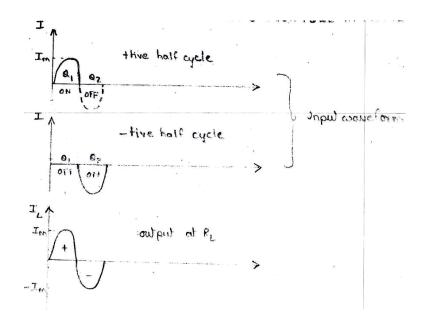

- 1) CLASS A (Conduction angle 0 to  $360^{\circ}$ )

- 2) CLASS B (conduction angle 0 to 180<sup>0</sup>)

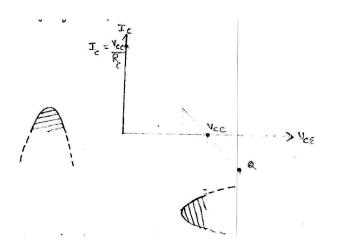

- 3) C LASS c (Conduction angle  $< 180^{\circ}$ )

- 4) CLASS AB (conduction angle grater than  $180^{\circ}$  & lesser than  $360^{\circ}$

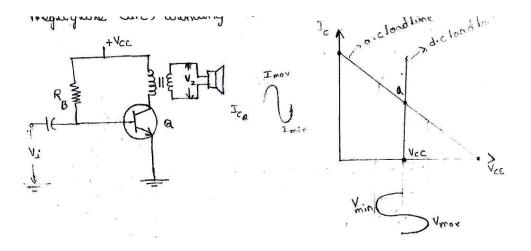

- 3) CLASSIFICATION BASED ON COUPLING

- 1) RC coupling

- 2) Transformer coupling

- 3) Direct coupling

- 4) CLASSIFICATION BASED ON LOAD

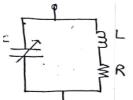

- 1) resistive

- 2) inductive

- 5) CLASSIFICATION BASED ON APPLICATION

- 1) VOLTAGE AMPLIFIER

#### 2) CURRENT AMPLIFIER

#### 3) POWER AMPLIFIER

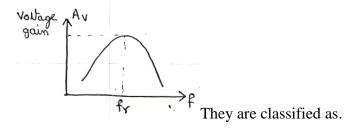

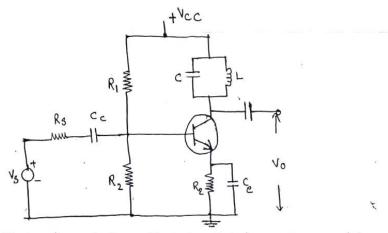

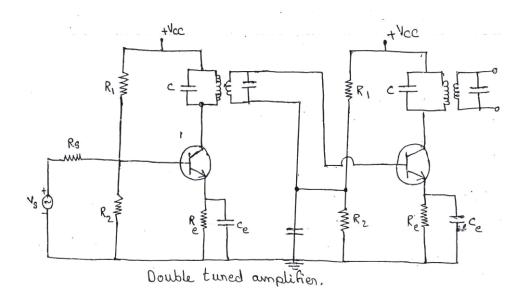

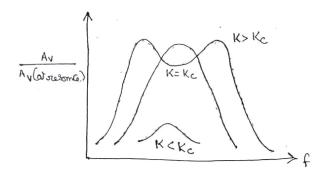

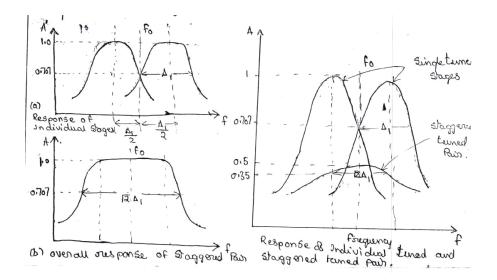

#### 4) TUNED AMPLIFIER

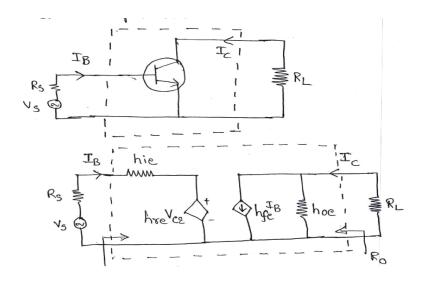

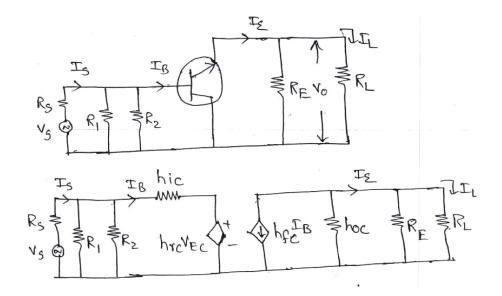

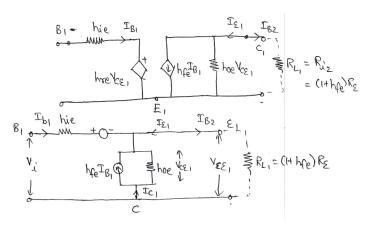

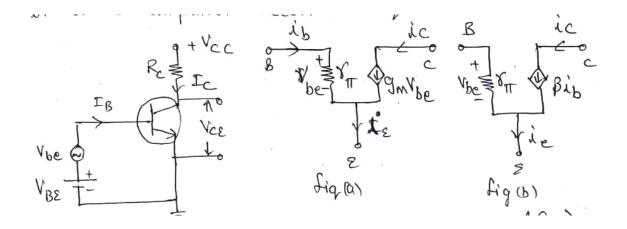

### TRANSISTOR HYBRID MODEL

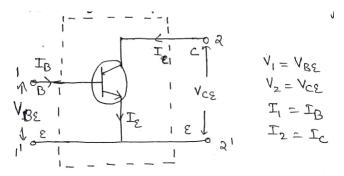

1) consider a BJT as two part device (ce configuration)

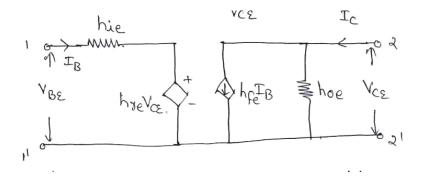

$$\label{eq:relations} \begin{split} h & - \text{ parameter equations} \\ V_1 &= h_{11} \ I_1 + h_{12} \ V_2 \\ I_2 &= h_{21} \ I_1 + h_{22} \ V_2 \\ \text{For CE configuration} \\ V_{BE} &= h_{ie} \ I_B + h_{re} \ V_{ce} \\ I_C &= h_{fe} \ I_B + h_{oe} \ V_{ce} \\ \text{Short circuit port } 22^1, \quad V_{ce} = 0 \\ \text{Input impendence } h_{ie} = \\ \text{Forward current gain } h_{fe} = \\ \text{Open circuit port } 11^1, \ I_B = 0 \\ \text{Reverse voltage gain } h_{re} = \\ \text{Output admittance } h_{oe} = \end{split}$$

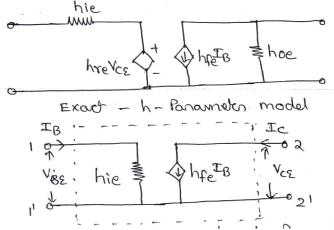

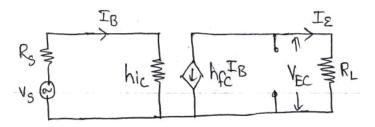

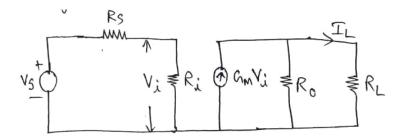

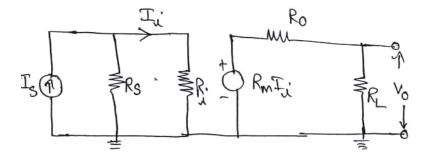

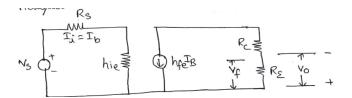

### Exact h- parameter small signal model

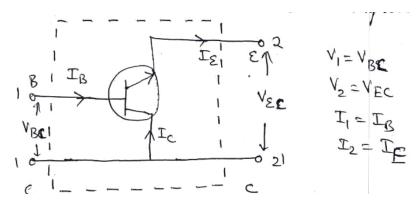

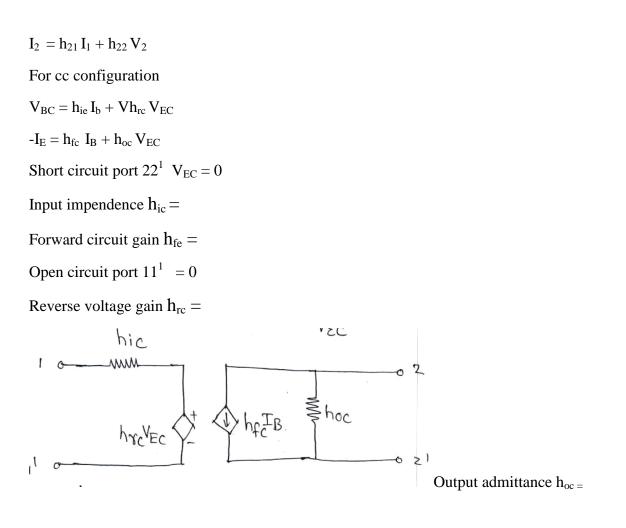

### 2) COMMON COLLECTOR CONFIGURATION

1) Consider a BJT as two port device (cc configuration)

H – Parameter equations

$$V_1 = h_{11} I_1 + h_{12} V_2$$

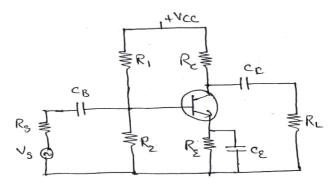

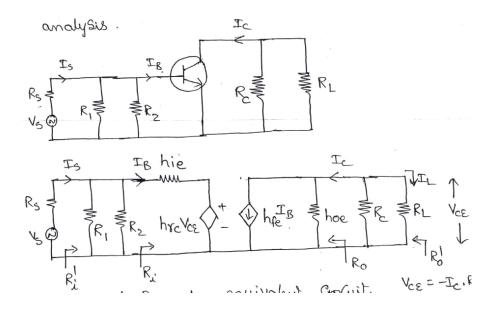

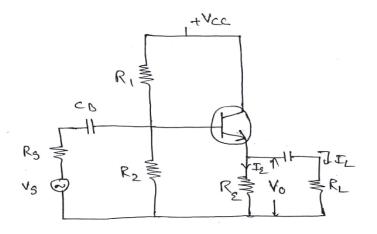

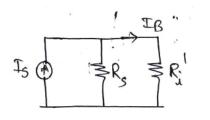

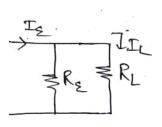

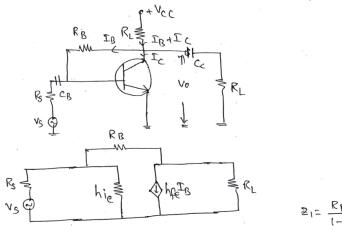

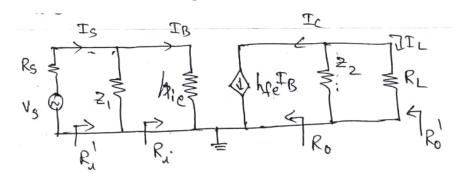

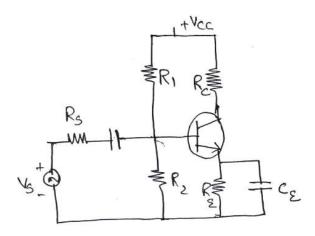

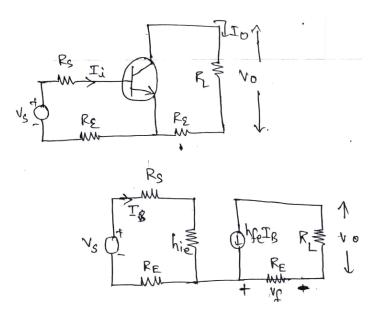

### 4) CE SINGLE STAGE AMPLITIER WITH R<sub>S</sub> & R<sub>L</sub>

### 1) Consider CE amplifiers

$$\begin{split} V_{BE} &= h_{ie} \, I_B + h_{re} \, V_{CE} \\ I_C &= h_{fe} \, I_B + h_{oe} \, V_{CE} \end{split}$$

2) A.C analysis

1) Current gain

$$A_{I==} \\ I_C &= h_{fe} \, I_B + h_{oe} \, V_{CE} \\ I_B \\ &= h_{fe} + h_{oe} \\ &= h_{fe} + h_{oe} \\ [ \ 1+h_{oe} \, R_L \ ] &= h_{fe} \end{split}$$

$\mathbf{I}_{\mathrm{B}}$

$$A_I = =$$

### 2) INPUT IMPENDENCE

$R_i = =$

Consider equation (1)

$$V_{BE} = h_{ie} I_{B} + h_{re} V_{CE}$$

$$V_{BE} = h_{ie} I_{B} + h_{re} (-)$$

$$= h_{ie} I_{B} + h_{re} (-)$$

$R_i = = h_{ie} + h_{re} A_{I \perp} R_{L \perp}$

### **3) VOLTAGE GAIN**

Consider input 100p (KVL)

$V_s$  -  $I_B\, R_s$  -  $I_B\, h_{ie\,-} h_{re}\, V_{CE}~=0$

Let  $V_S = 0$ ,

Using above equation

Output resistance R<sub>0</sub> =

#### **3) SIMPLIFIED H- PARAMETER MODEL**

In practice the voltage ' $h_{re} V_{ce}$ ' is very less value when compared to  $I_B h_{ie}$ , hence  $h_{re} V_{CE}$  is neglected similarly the load resistance  $R_L$  is selected minimum times lesser than (1/hoe)  $\Omega$ , hence hoe is neglected.

By removing  $h_{re} V_{CE}$  and  $h_{oe}$  simplified model is obtained. The approximate values are very near to the exact values.

Approximate h – parameter model

|                     | EXACT                             |           | IMPLIFIED      |

|---------------------|-----------------------------------|-----------|----------------|

| 1) Current gain     | $A_I =$                           | $A_{I} =$ |                |

| 2) Input resistance | $R_i = h_{ie} + h_{re} A_{I} R_L$ |           | $R_i = h_{ie}$ |

- 3) Voltage gain  $A_v = A_v =$

- 4) output admittance  $Y_0 = h_{oe} Y_0 =$

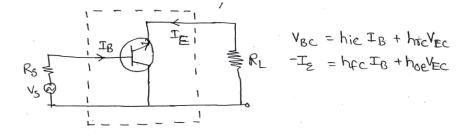

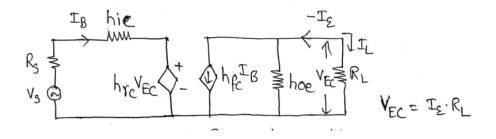

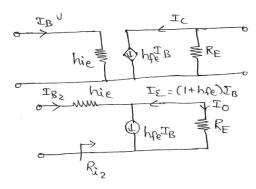

#### SIMPLIFIED C.C CONFIGURATION

1) consider common collector configuration

Exact – h- parameter model.

### Simplified – h- parameter model.

### 2) CURRENT GAIN

$$\begin{split} A_{I} &= \\ -I_{E} &= h_{fc} \ I_{B} + h_{oe} \ V_{EC} \\ -I_{E} &= h_{fc} \ I_{B} + h_{oe} \ I_{E} \ R_{L} \\ - \ h_{fc} \ I_{B} &= I_{E} + h_{oe} \ I_{E} \ R_{L} \\ - \ h_{fc} \ I_{B} &= I_{E} \ (1 + h_{oe} \ R_{L}) \\ A_{I} &= \\ \end{split}$$

### **3) INPUT RESISTANCE**

$R_i \;=\; =$

Consider eq (1)  $V_{BC} = h_{ie} I_B + h_{re} V_{EC}$

$$V_{BC} = h_{ic} I_B + h_{rc} V_{EC}$$

$\mathbf{I}_{\mathbf{B}}$

$$= h_{ic} I_{B} + h_{rc}$$

$$R_{i} = = h_{ic} + h_{re} A_{I} \qquad h_{ic} + 1. (1 + h_{fe}) R_{L}$$

### **3) VOLTAGE GAIN:**

$A_V = = =$

### $\mathbf{I}_{\mathrm{B}}$

Consider eq:

$= A_{v} = A_{v} =$

>>

Neglected

$A_v =$

$A_v = 1$

4) OUTPUT RESISTANCE

$R_0 = =$

KVL to input loop

$V_{s} - I_{B} R_{s} - I_{B} h_{ic} - h_{rc} V_{EC} = 0$

Let  $V_S = 0$ ,

$$- I_B R_S - I_B h_{ic} - 1. V_{EC} = 0$$

- V<sub>EC</sub> = I<sub>B</sub> (R<sub>S</sub> + h<sub>ic</sub>)

R<sub>0</sub> = =

R<sub>0</sub> =

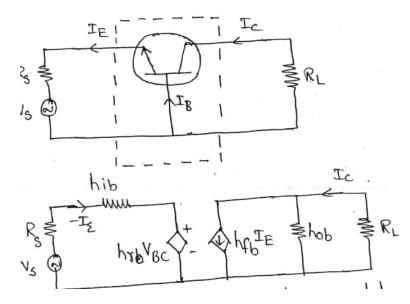

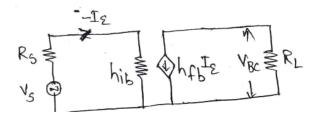

### 6) SIMPLIFIED CB CONFIGURATION.

1) Consider CB configuration as shown below.

### **Exact – h- parameter model**

### Simplified hybrid model

1) current gain (A $_{\rm I}$ ).

=

$A_{I} \ 1$

2) INPUT RESISTANCE (R<sub>i</sub>)

$R_i \ = \ = \ =$

$R_i \; = \;$

### 3) VOLTAGE GAIN (Av)

$A_V = = =$

$A_V =$

### 4) OUTPUT RESISTANCE (

= =

=

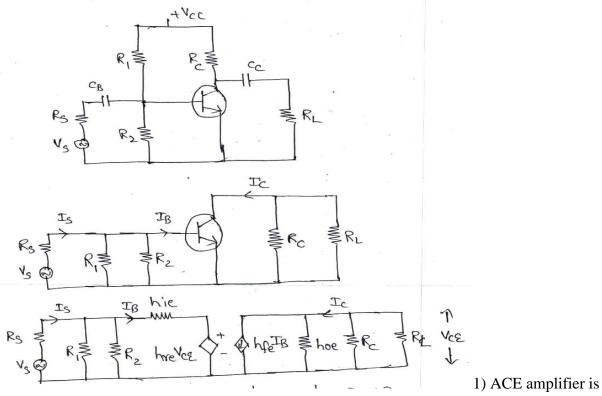

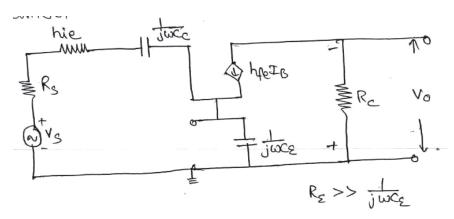

### 7) CE AMPLIFIER WITH R<sub>E</sub> & CE ( BY PASS CAPACITOR)

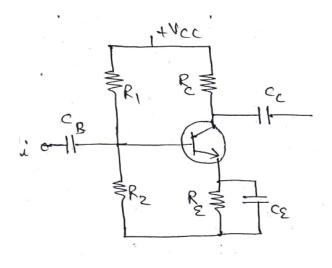

1) A single stage CE amplifier is shown blow.

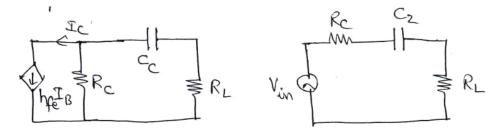

### 2) A.C analysis

$\underline{\mbox{h-Parameter equivalent circuit}} \quad V_{CE} = \mbox{-} I_{C.}$

$= \mathbf{R}_{\mathrm{L}} \, \| \mathbf{R}_{\mathrm{C}}$

### 3) CURRENT GAIN AI

$A_{I}= \\ =$

$\text{-}I_{C} = h_{fe`1\;2347890=} \;\; I_{B} + h_{oe} \, V_{CE}$

$I_{B}$

$= h_{fe} + h_{oe}$

$$\begin{split} + & h_{oe} = h_{fe} \\ + & [ 1+h_{oe} = h_{fe} ] \\ = \\ A_I = = \\ \hline A_I = \\ \hline A_I$$

### 5) VOLTAGE GAIN:

$A_V=~=~=~$

$= h_{\rm fe} + h_{\rm oe} \ .$

$I_{B} \\$

$A_V =$

$A_V =$

6) OUTPUT RESISTANCE

### 7) FOR CIRCUIT.

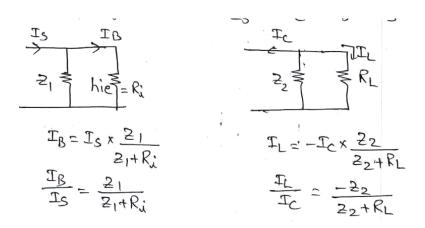

a) Current gain

$A_{IS}= \\ =$

=

$I_B = I_S \qquad \qquad I_L = \text{-}I_C$

=

$A_{IS} =$

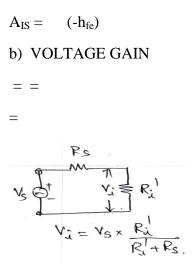

**b) VOLTAGE GAIN.**

c) Input resistance

$= \mathbf{R}_1 \mathbf{R}_2 \mathbf{R}_i$

4) Output resistance

$= R_L R_C R_O$

### 8) CE AMPLIFIER with EMITTER (short circuited = 0)

shown below.

$V_{CE} = \text{-}I_{C}\text{. , } = R_C \ R_L$

[NOTE: The previous circuit and this circuit are same]

- 1)  $A_I = \rightarrow A_{IS} =$

- $2)=\ + \qquad \rightarrow = R_1 \ R_2 \ R_i$

- 3)  $A_v = \rightarrow A_{VS} = A_v$

- $4) = \rightarrow = R_L R_C R_{O.}$

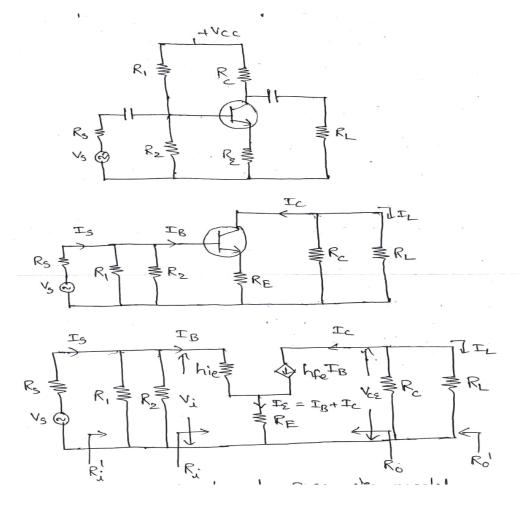

### CE AMPLIFIER WITH R<sub>E</sub> RESISTOR.

1) A CE amplifier with only  $R_E$  resistance is considered

### Approximate h- parameter model

$$\begin{split} I_E &= I_B + I_C = I_B + h_{fe} \, I_B = I_B [1 + h_{fe}] \\ V_{CE} &= -I_{C^*} \; , \; = R_L \; R_C \end{split}$$

. . . . . . .

A.C analysis for transistor.

2) Current gain  $A_I$

$A_I = \; = \;$

A<sub>I</sub> -

3) Input resistance

$R_i= \\ =$

$V_{BE}\!=\!\!+I_E\,R_E$

$V_{BE}$  =+ (1+h\_{fe}) R<sub>E</sub>

$R_i = \; = + \; ( \; 1 + \; ) \; R_E$

[Very high input resistance]

### 4) VOLTAGE GAIN

$A_V=~=~=~$

5) Output Resistance

$R_O = =$

A.C analysis for circuit

1) Current gain

=

$$I_L = -I_C$$

$A_{IS} =$

2) VOLTAGE GAIN

$A_{VS} = AV$

3) INPUT REISTANCE

$= R_1 R_2 R_i$

4) OUTPUT RESISTANCE

$= R_L R_C R_O$

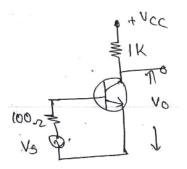

# 10) COMMON COLLECTOR (OR) EMITTER FOLLOWER (OR) VOLTAGE FOLLOWER

1) in the emitter or voltage follower circuit the output for voltage follow is input voltage hence named voltage follower. The voltage across  $R_E$  resistor is output voltage.

2) The voltage gain of this circuit is amity. Hence if can be used as voltage buffer circuit.

3) The emitter follower circuit has high current.

4) The input resistance of this circuit is very high.

5) A emitter follower circuit is shown in below.

$V_{EC} = \textbf{-}I_{E\textbf{-}} \ , \ = R_E \ R_L$

#### 6) AC analysis for transistor

- a) Current gain  $A_I =$

- $I_E = h_{\rm fc} \; I_B + h_{\rm oc} \; V_{EC}$

- $I_E = h_{\rm fc} \; I_B + h_{\rm oc} \; I_E$

$= h_{\rm fc} + h_{\rm oc}$  $-h_{\rm fc} = + h_{\rm oc}$  $[1 + h_{\rm oc}] = - h_{\rm fc}$

$A_I = = = 1 +$

### **B) INPUT RESISTANCE**

$R_i = =$

$V_{Bc} = h_{ic} I_B + h_{rc} V_{EC}$

$V_{Bc}\ = h_{ic}\ I_B + h_{rc}\ .I_E$

$= h_{ic} + h_{rc}$  .

$R_i = \ = \ h_{ic} + h_{rc} \ . A_I = h_{ie} + 1 \ (1 + h_{fe} \ )$

### **C) VOLTAGE GAIN**

$A_V = = =$

= = = = =

- neglected.

,

$A_V = = 1$

$V_o = V_i$ , output voltage follows input voltage.

### D) OUTPUT RESISTANCE. (R<sub>0</sub>)

$R_o =$

### 7) A.C analysis for circuit.

a) Current gain

$A_{IS}= \\ =$

$\equiv$

$$I_L = I_E$$

$A_{IS} =$

### **b) VOLTAGE GAIN**

$A_{VS} = =$

=

=

$A_{VS} = A_V$

c) Input resistance

$= R_1 R_2 R_i$

b) Output resistance

$= R_L \, R_E \ R_O$

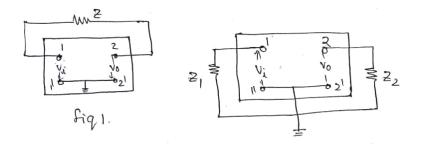

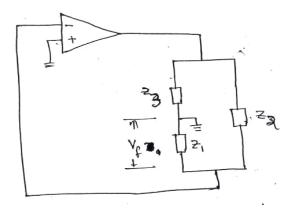

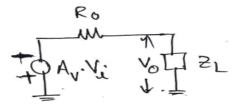

### **MILLERS THOREM.**

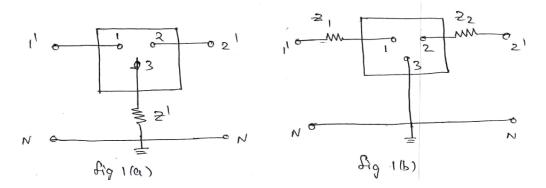

1) According to millers theorem, when even a resistor is connected between two nodes fig (1), it can be replaced as shown in fig (2)

Where  $Z_1 & Z_2$  are given by

$$Z_1=\ ,\ \ Z_2=\ \ Z$$

$$K= = A_V$$

Where  $V_i$  is voltage at node 1 and  $V_0$  is voltage at node 2.

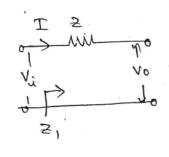

### 2) proof

Consider a circuit shown in fig.3

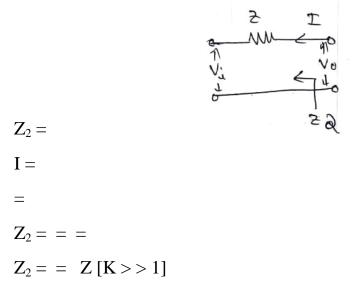

### $Z_1 =$

I =

=

$Z_1 = =$  $Z_1 = =$

Consider a net work shown in fig . 4

### 12) DUAL OF MILLER'S THWOREM

Consider a network shown in fig 1 (a) now  $Z^1$  is the impendence between node 3 and ground N. according to dual of millers theorem  $Z^1$  can be split into  $Z_1$  and  $Z_2$  such that  $Z_1$  is placed in mesh 1 and  $Z_2$  is added to mesh 2 as shown in fig 1 (b) and node 3 is grounded.

$$A_{I} = ,$$

$Z_{2} = Z^{1}$

$Z_{1} = Z^{1} (1 - A_{I})$   $Z_{2} Z^{1}$

#### COLLECTOR BASE BIAS CE AMPLIFIER.

1) A CE amplifier with collector base bias is shown below.

Miller Theorem. I

Using miller theorem.

2) A.C analysis for transistor.

a) Current gain

b) input resistance

c) Voltage gain

$A_I= \ = \ = \ \text{-}$

= = = =

= = =

=

=

$$= Z_2$$

b) Output resistance  $R_0 =$

3) A.C analysis for circuit

a) current gain

= =

C) Input resistance ()

$$= Z_1 R_i$$

d) Output resistance

$= R_L \ Z_2$

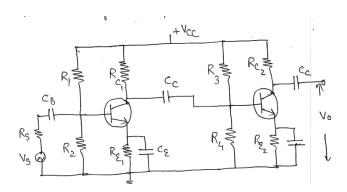

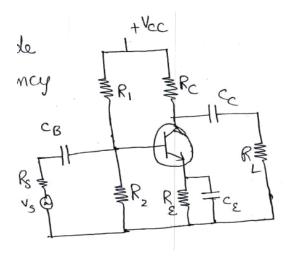

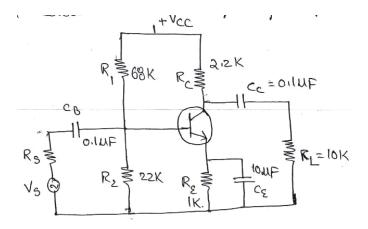

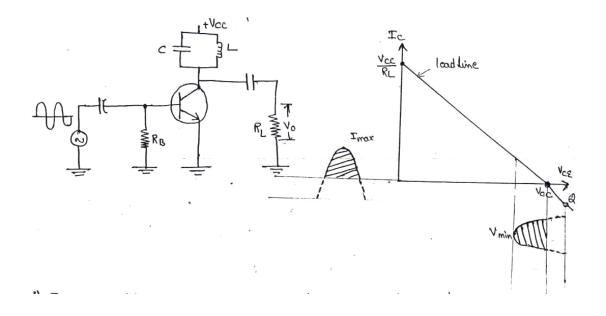

RC COUPLED CE AMPLIFIER DESIGN.

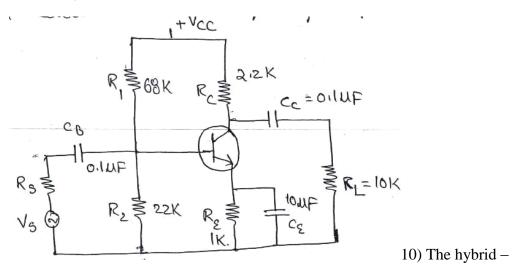

1) A RC coupled CE amplifier is shown below

#### ASSIGNMENT – I

- 1) explain about single stage CE amplifier. Explain function of each component.

- 2) Explain CB, CE, CC configuration with h- parameter analys and draw equivalent circuits.

- 3) Explain how h- parameters can be obtained from the transistor characteristics.

- 4) list the benefits or h- parameter.

- 5) derive the expressions for  $A_{I_{1}}A_{IS_{1}}A_{V_{2}}A_{VS_{1}}R_{i_{1}}R_{i_{1}}^{-1}$ ,  $R_{0_{1}}R_{0_{1}}^{-1}$  for CE amplifier.

- 6) give analysis for CE amplifier with  $R_E$

- 7) draw the circuit of CB amplifier and its h- parameter equivalent circuit.

- 8) explain follower circuit.

(or)

Explain voltage follower circuit

(or)

Given analysis of C.C amplifier.

9) state and explain milter's theorem and its dual.

10) design a single stage RC coupled amplifier.

### ASSIGNMENT - 2

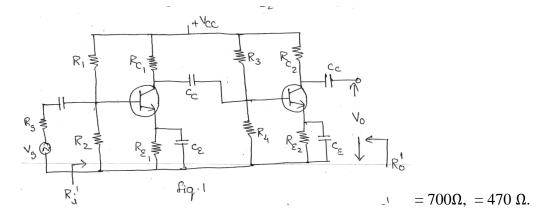

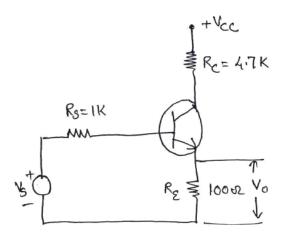

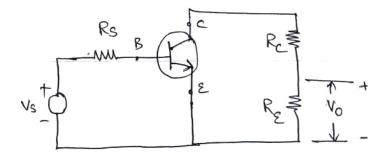

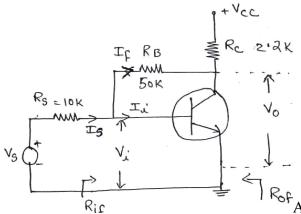

#### CE AMPLIFIER

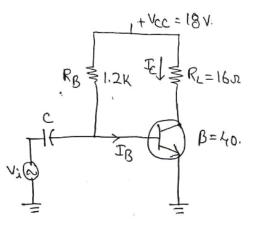

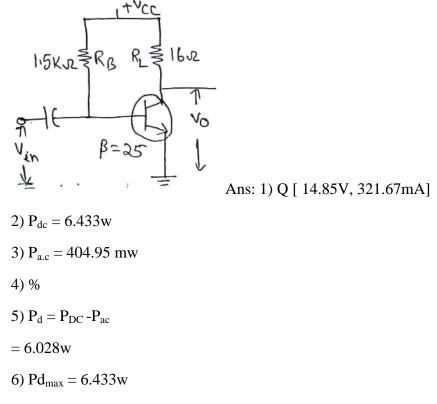

1) Consider a single stage CE amplifier with

$R_{S} = 1k, R_{1} = 50k, R_{2} = 2k, R_{c} = 2k, R_{L} = 2k, h_{fe} = 50,$

as shown in fig 1. Find  $A_V$ ,  $A_{VS}$ ,  $A_I$ ,  $A_{IS}$ ,  $R_i$ ,  $R_i^1$ ,  $R_0$ ,  $R_0^1$ ,

$$A_{\rm I} = -50$$

$$A_{IS} = -15.9$$

$$A_{\rm V} = -45.45$$

$A_{VS} = -18.71$

$$R_{I} = 1.1 K$$

$R_0 = 40K$

$R_{I}^{\ 1}=700\Omega$

$R_o{}^1 = 1 \ k$

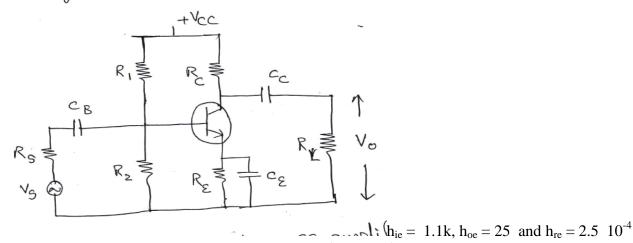

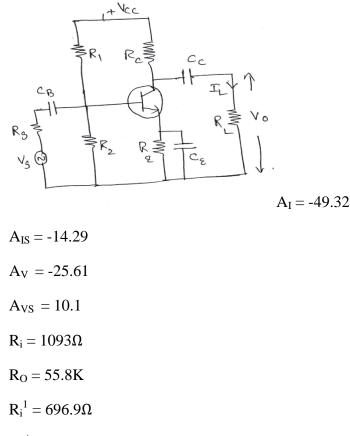

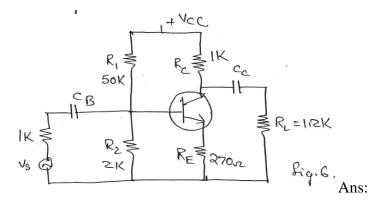

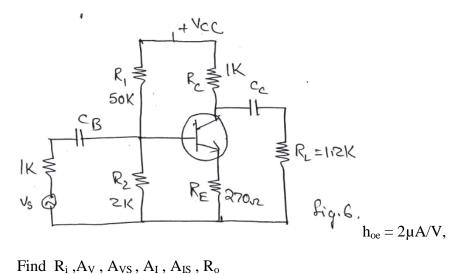

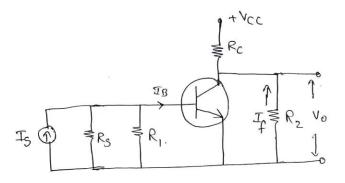

2) Consider a single stage CE amplifier with Rs = 1 K $\Omega$ , R<sub>1</sub> = 50K $\Omega$ , R<sub>2</sub> = 2K, R<sub>c</sub> = 1K $\Omega$ , R<sub>L</sub> = 1.2 k $\Omega$ , h<sub>fe</sub> = 2.5 50, h<sub>ie</sub> = 1.1K, h<sub>oe</sub> = 25 $\mu$ A/V, h<sub>re</sub> = 2.5 10<sup>-4</sup>, as shown in fig.2.

Find A<sub>I</sub>, A<sub>IS, Ri</sub>, A<sub>V</sub>, A<sub>vs</sub>, R<sub>0</sub>,

$R_{\rm o}{}^1=540\Omega$

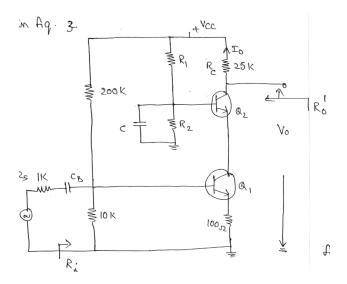

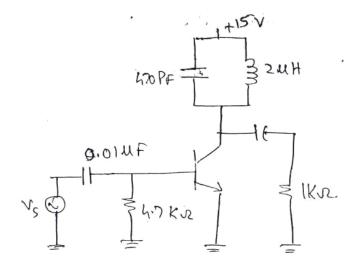

3) the transistor amplifier shown in fig. 3 has h- parameter typical values  $h_{ie} = 1100\Omega$ ,  $h_{fe} = 50$ ,  $h_{re} = 2.5 \ 10^{-4} h_{oe} = ..$  Find  $A_{VS}$ ,  $A_{IS}$ ,  $R_o^{-1}$ ,  $R_i^{-1}$

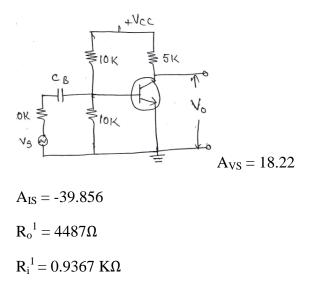

4) the transistor used in the circuit show in fig 4, has following values  $h_{ie} = 500\Omega$ ,  $h_{re} = 60$ ,  $h_{oe} = 1/40k$ , calculate  $R_i$ ,  $R_i^{-1}$ ,  $A_V$ ,  $A_{VS}$ ,  $A_I$ ,  $A_{IS}$ ,  $R_o$ ,  $R_o^{-1}$

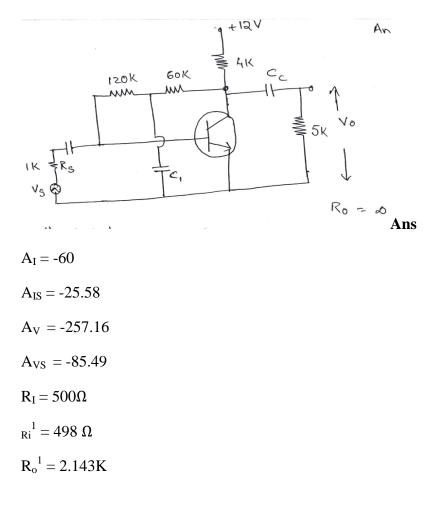

### 5) For the circuit shown in fig .5:

### Find, $\mathbf{R}_i$ , $\mathbf{R}_i^1$ , $\mathbf{R}_o$ , $\mathbf{R}_i^1$ , $\mathbf{A}_{VS}$ , $\mathbf{A}_I$

Use typical values.

#### Ans:

$$A_{\rm I} = -200$$

$A_{\rm V} = -200$

$A_{VS} = -71.13$

$R_i = 4K$

$$_{\rm Ri}^{1} = 2.76 {\rm K}$$

$R_o^1 = 4K$

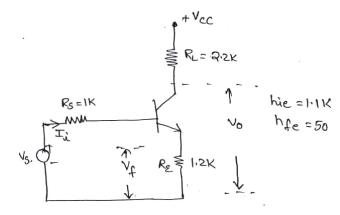

### CE amplifier with $R_E$

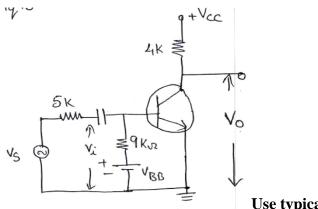

6) Find current gain, voltage gain, input and output resistance for unbypassed CE amplifier. In fig 6.

$A_I=-50$  $A_{IS} = -2.6$  $A_V = -1.834$  $A_{VS} = -1.15$  $R_i = 14.87$  $_{Ri}^{1} = 1.7K$  $A_{I} = -0.454$  $R_o{}^1 = 545.45\Omega$

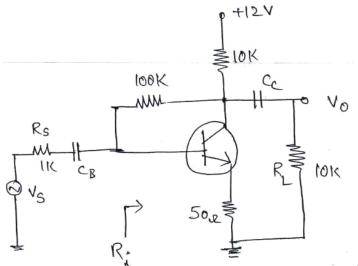

7) For fig.6 use typical values of h parameter and Rs = 10K,  $R_1 = 100K$ ,  $R_2 = 10K$ ,  $R_e = 1K$ ,  $R_L = 10K$ ,  $R_{\rm c} = 10K$ ,  $R_{\rm c}$ 5k.

Find  $R_i$ ,  $R_i^1$ ,  $A_V$ ,  $A_{VS}$ ,  $A_I$ ,  $A_{IS}$ ,  $R_o$ ,  $R_o^1$

Ans: (A<sub>I</sub>=-43.45, -7.24, -4.77, -2.05, 45.48K, 7.576K, 215K, 4.8K)

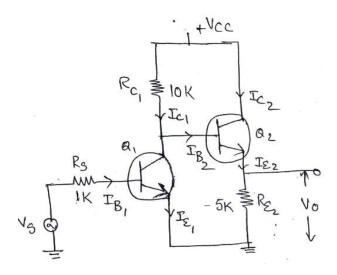

#### **CC** Amplifier

8) A common collector circuit shown in fig .8 has the following parameters,  $Rs = 600\Omega$ ,  $R_1 = 27K$ ,  $R_2 = 27K, R_e = 5.6K, R_L = 47k\Omega. \ h_{ie} = 1K, h_{fe} = 85,$

Find  $R_i$ ,  $A_V$ ,  $A_{VS}$ ,  $A_I$ ,  $A_{IS}$ ,  $R_o$

Ans:

$A_{I} = 86$

$A_{IS} = -0.273,$

$$A_V = 0.997,$$

$A_{VS} = 0.953$

$R_i = 431.33K$

$R_i^{1} = 13.09K$

$R_o = 18.3\Omega$

$R_o^{1} = 18.23\Omega$

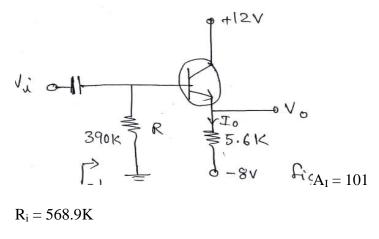

9) The circuit shown in fig 9. Has  $h_{fe} = 100$ ,  $h_{ie} = 3.37 K\Omega$  neglected  $h_{re}$ ,  $h_{oe}$ , find  $R_i^{-1}$ ,  $A_V$ ,  $A_L$

$R_i^{\ 1} = 231.39K$

$A_V = 0.994,$

$A_{IS} = 41$

### **MILLER'S CIRCUIT**

10) Find,  $A_{I}$ ,  $A_{VS}$ ,  $R_i$ ,  $R_o$  for circuit shown

in fig .10

$A_{I} = -8.25$

$R_i^1 = 1.048K$

$R_0^{1} = 5K$

$A_{VS} = -69.8$

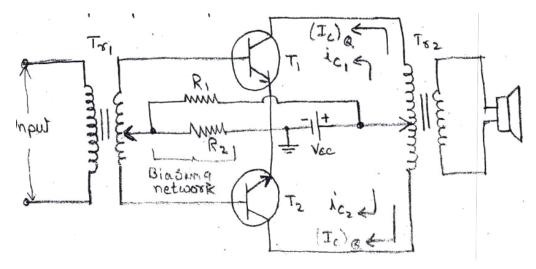

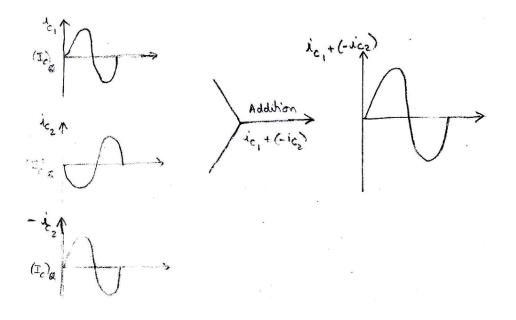

### MULTISATAGE AMPLIFIERS

#### 1) INTRODUCTION

A single stage amplifier provides amplification of for a weak signal, but the gain of single stage may not be sufficient for contain applications. Under such cases we go for multistage amplification i.e., amplifying 'a signal again and again. Sometimes the impendance matching at source and load is not proper in such matching at source and load is not proper, in such cases using a cascaded amplifier, the above requirement can be achieved.

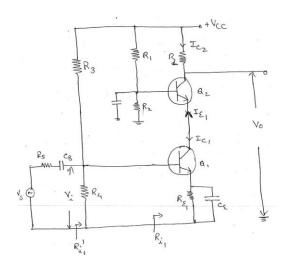

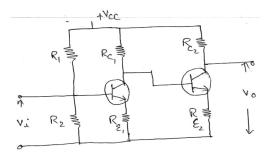

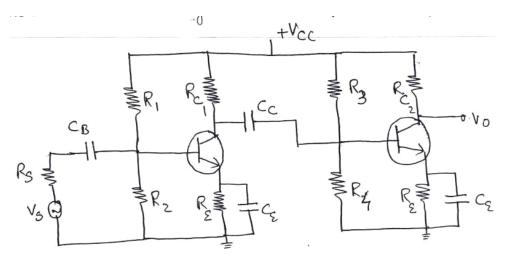

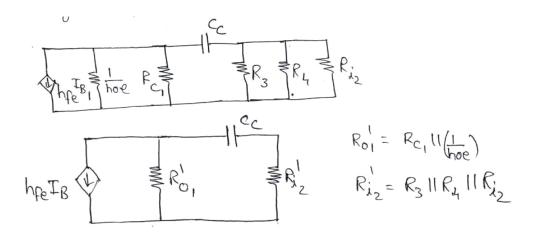

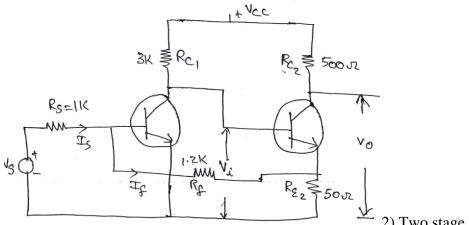

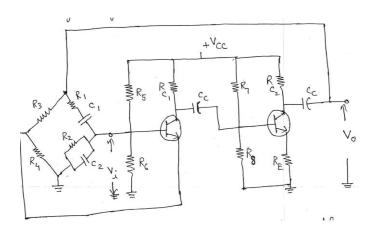

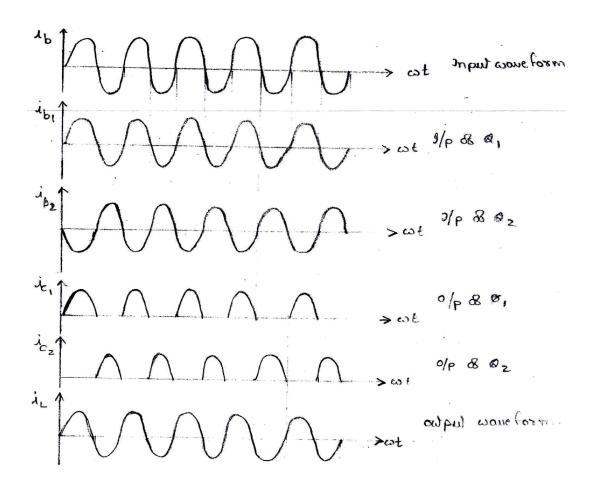

#### 2)TWO STAGE RC COUPLED CE-CE CASCADED AMPLIFIER.

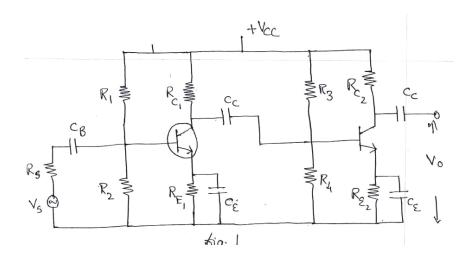

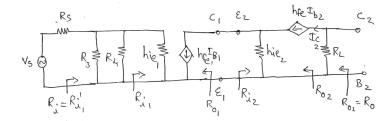

1) A CE -CE cascaded amplifier is shown below. fig.1

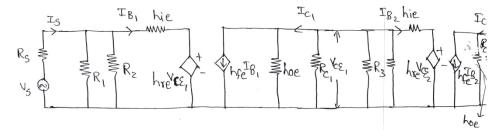

h- Parameter equivalent circuit for CE – CE cascade amplifier is shown below. Fig 2.

# 2) Analysis of second stage.

1) Current gain

$A_{I2}=\ \textbf{-}=$

2) Input resistance

= +

3) Voltage gain

=

## 3) Analysis of first stage.

The input resistance is load resistance for first stage.

$= = \mathbf{R}_3 \parallel \mathbf{R}_4 \parallel$

$= \| = \| \| \|$

1) Current gain

= =

2) Input resistance

= +

3) Voltage gain

=

#### 4) OVERALL GAIN.

1) Total voltage gain

$A_V =$

$= A_V$

2) Input resistance

$= \mathbf{R}_1$

3) output resistance

=

4) Current gain A<sub>I</sub>

For finding current gain, loading effect must be considered. Hence the gain is calculated as shown below.

$A_I = = =$

$A_I = \ \, \text{-} \,$

With source resistance  $R_S$

$\begin{array}{l} A_{IS} = \\ A_{IS} = \\ A_{IS} = \\ A_{IS} = (- (- \\ = R_1 \\ = R_3 \parallel R_4 \parallel \\ = \\ = \\ = \\ = \\ = \end{array}$

3) TWO – STAGE RC COUPLED CE-C.C CASCADED AMPLIFIER.

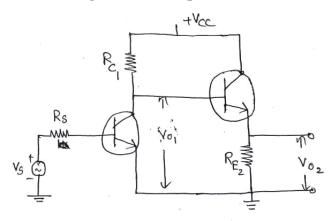

1) A two stage CE-C.C amplifier is shown below in fig .1

#### h- Parameter model of two stage CE - CC amplifier

# 2) A.C analysis of second stage.

#### 1) Current gain

$$A_{I2} = -$$

2) Input resistance

= +

3) Voltage gain

=

# 3) A.C analysis of first stage.

1) Current gain

= ,

= =

2) Input resistance

= +

3) Voltage gain

=

# 3) Over all gain:

1) Voltage gain (A<sub>V</sub>)

$A_V =$

$= A_V$

2) Current gain (A<sub>I</sub>)

$A_I = \; = \;$

$A_{I} =$

3) Input resistance R<sub>i</sub>

=

4) Output resistance R<sub>o</sub>

$R_{o} = \|$

= -

$R_o =$

4) CE – CB CASCODE AMPLIFIER.

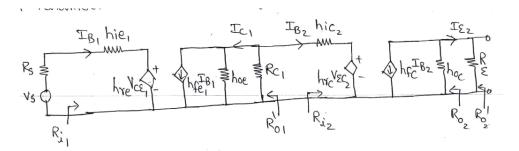

# h- Parameter equivalent for CE – CB amplifier

# 2) A.C analysis of second stage (CB)

### 1) Current gain

$A_{I2} = = 1$

2) Input resistance

=

3) Voltage gain

=

# 3) A.C analysis of first stage (CE)

1) Current gain

= -

2) Input resistance

=

3) Voltage gain

=

# 4) Over all gain:

```

1) Voltage gain (A<sub>V</sub>)

```

$A_V =$

=

2) Output resistance

$R_O = \|$

3) Input resistance

$R_i \hspace{-0.5mm} = \hspace{-0.5mm} |\hspace{-0.5mm}| \hspace{-0.5mm} |\hspace{-0.5mm}|$

4) Current gain

$A_{IS} = =$ = = -1 = -1 = , = ||.  $A_{IS} = (-1)$

#### $A_{IS} =$

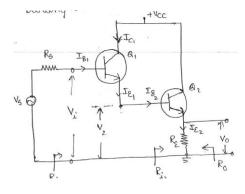

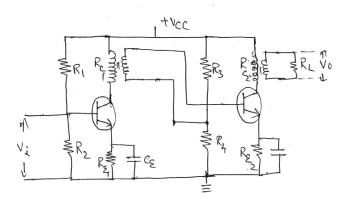

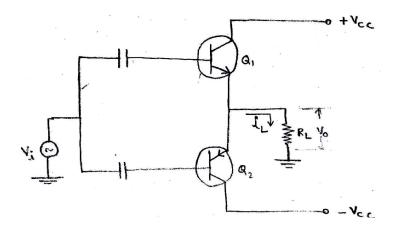

5) DARLINGTON PAIR [high input resistance circuit]

1) The common collector circuit has high input impendence about 200k  $\Omega$  to 300k $\Omega$ . when considered with biasing resistors, for a emitter follower has input impendence lers 500k $\Omega$

2) The input impendence of the circuit can be improved by direct coupling of two stages of emitter followers amplifier. By using following two methods.

1) Using direct coupling (Darlington pair)

2) Using bootstrap technique

3) A Darlington pair is shown below.

4) A.C analysis of second stage.

#### 1) Current gain

= =

=

#### Input resistance

= - - -= = + = + 3) voltage gain

= 1

5) A.c analysis of first stage.

The output resistance of first stage is input resistance of second stage. (= . As is very high exact model of transistor h- parameter is considered.

1) Current gain (

= =) = + = +) +) Using eq of =) = )

[1+=(1+)

=

= =

= =

2) INPUT RESISTANCE R<sub>i</sub>

$R_i =$

KVL to input loop  $R_i$

- -

- - u

$V_i = h_{ie} + h_{re}$  -

$$= h_{ie} + h_{re} - (.)$$

=  $h_{ie} - - (.)$

$V_i = h_{ie} +$

=  $= h_{ie} + .$

=  $h_{ie} + .$

6) over all gain

1) Current gain =

=

2) overall voltage gain

$A_V =$  $A_V =$ = , >>

3) output impedance (

=

= +

### 6) Comparison of emitter follower and Darlington

$\begin{array}{cc} C.C & Darlington \\ R_i & R_i = (\ 1 + \ h_{fe}) \ R_E & R_i = \\ (168 k \Omega) & (1.65 m \Omega) \end{array}$

$A_{I} \qquad \qquad A_{i}=1+ \ h_{fe}=51 \qquad \qquad A_{i}=\ =500$

### 7) METHODS OF COUPLING

When cascading amplifier is done, coupling of one stage to one stage is done based following 3 methods.

1) Direct coupling

#### 2) RC coupling

3) Transformer coupling

#### 1) DIRECT COUPLING

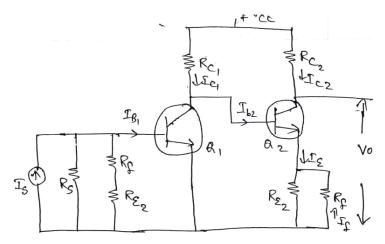

1) A two stage direct coupled amplifier is shown below.

2) the output of first stage is directly connected to next stage input.

3) The d.c collector current of first stage passes to input of next stage is altered. This effects the biasing condition of second stage amplifier.

4) The low frequency response of this amplifier is gold, but hight frequency response is poor because of stray capacitance.

5) The change in temperature disturbs the  $V_{BE}$  and B of transistor, by which outout collector current is varied. The output is distorted.

#### 2) RC COUPLED AMPLIFIER.

1) A RC coupled amplifier is shown below.

2) The output of first stage amplifier is connected to input of next stage amplifier through a capacitor and resistor.

3) The capacitor ' $C_C$ ' blocks the d,c components therefore a point is maintained stable for both amplifier.

4) The frequency response is wide band in nature hence this amplifier provides stable gain for AF applications.

6)At very low frequency the coupling capacitor  $C_C$  effects the gain and at very high frequency gain falls to stray capacitance.

#### 3) TRANSFORMER COUPLING.

1) A transformer coupled amplifier is shown in fig below

2) The output of first stage amplifier is connected to input of next stage through a transformer.

3) When impendence matching is criteria then this is achieved by proper selection of transformer between cascaded stage.

4) the d.c conditions of both stage are stable as the coupling does not effect Q point.

5) The frequency response of this amplifier is poor when compared to RC coupled amplifier.

6) The intertwining and leakage indolence does not allow amplifier to amplify the signals of different frequencies. Equally well.

7) these amplifiers when provided with a capacitor in shunt with transformer winding, faction as resistance circuit and provide very large or high gain at that resonant frequency.

8) The d.c resistance of the transformer winding is kept low. So that power loss is lers.

#### ASSIGNMENT-1

1) what is need for cascading ? explain

2) Draw and explain the block diagram of two stage CE -CE cascaded amplifier

3) Derive the overall gain of two stage cascaded

Derive the overall current and voltage gain Input and output resistance of CE-CE cascaded amplifier.

4) Find, A<sub>I</sub>, A<sub>v</sub>, ,, for CE –CE cascaded amplifier

5) Find, A<sub>I</sub>, A<sub>v</sub>, ,, for CE –CB or cascade amplifier

6) Explain any one circuit which is used to improve the input impendence of the amplifier.

7) What is Darlington connection ? derive current gain and input resistance.

8) What are draw backs of a Darlington amplifier, how it overcomes in Boot strap CC amplifier. Explain with neat diagram.

9) Compare emitter follower and Darlington pair with respect different A<sub>I</sub>, A<sub>v</sub>, R<sub>i</sub>, R<sub>O</sub>,

10) What are different types of coupling used in cascading of amplifiers? Explain.

## ASSIGNMENT – 2

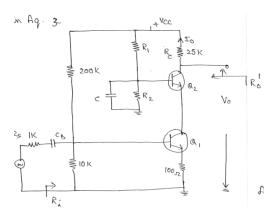

#### **CE-CE cascading.**

1Find  $A_V$ ,  $A_{VS}$ ,,, consider – h- parameter typical values, for a CE-CE cascaded amplifier (fig .1)

$R_1 = 22k\Omega, R_2 = 3.3 \ k\Omega, \ = 6 \ k\Omega \ , = 1k\Omega, R_3 = 16 \ k\Omega \ R_4 = 6.2 \ k\Omega, R_S = 1.1k.$

$(A_V = 1112.39, A_{VS} = 466.73, = 795.18\Omega = 700K)$

2) Find  $A_V$ ,  $A_{VS}$ ,, for circuit shown in fig.1 given  $R_1 = 200k$ ,  $R_2 = 20k = 15k$ ,  $= 100\Omega$ ,  $R_3 = 47 k$ ,  $R_4 = 4.7k$ ,  $R_S = 1k$ , = 4k,  $= 330 \Omega$ .

Consider h- parameter typical values.

Ans  $(A_V = 6123.45, A_{VS} = 3248.6, = 1.13k, = 4K)$

CE -CC cascading.

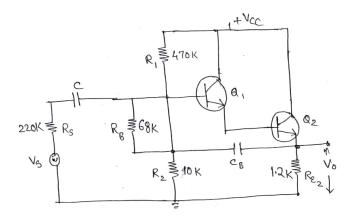

3) Find over all voltage and current gain, , for shown in fig 2.

Ans (A<sub>I</sub> = -76.56, A<sub>V</sub> = -216.5, A<sub>VS</sub> = -138.28, = 1.76k, = 199.69 $\Omega$ )

4) for the circuit shown in fig.2  $\,$  find  $A_{VS}, A_{IS} \, h_{fe}$  = 76,  $h_{ie}$  = 1.5k,  $h_{re}$  =  $h_{fe}$  = 0.

$= 10k, = 5k, R_S = 1k$

Ans  $(A_{VS} = -295.2, A_{IS} = -58.52)$

$$CE - CB$$

5) Calculate  $A_{I},\,A_{V},\,A_{VS},\!,\!,$  for cascade circuit shown in fig.3

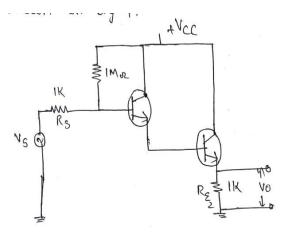

#### DARLINGTON PAIR.

6) Find  $R_i$ ,  $A_{VS}$ ,  $A_{IS}$ ,  $R_O$  for Darlington pair circuit shown in fig.4

Ans  $(A_{IS} = 889.23, A_{V} = 0.989, A_{VS} = 0.987, = 10.76\Omega R_i = 0.89M\Omega)$

7) For the circuit shown in fig.5 calculate,  $A_I$ ,  $A_V$ ,  $h_{fe} = 50$ ,  $h_{ie} = 1.1k$ ,  $h_{re} = 2.5 \ 10^{-4}$ ,  $h_{oe} = 25 \ A/V$ .

Ans  $A_V = 0.9918$ , = 2.02M,  $= 22.96 \Omega$ .

= 51, = 0.258, =

**BOOSTRAP CIRCUIT.**

8) For the circuit shown in fig 6. Calculate  $A_V$ ,  $A_{VS}$ ,  $R_O$  consider typical values of h-parameter.

Ans  $(A_V = 0.979) = 286 \text{ k}$ ,  $= 92.28 \Omega A_{VS} = 0.781$ , = 0.979, = 51.

#### 9) For fig .6, calculate, A<sub>V</sub>, A<sub>VS</sub>,,R<sub>i</sub>

### $R_{S} = 10k, R_{1} = 100k, R_{2} = 10 k, R_{B} = 50k, = 10k,$

Ans

$(A_V = 0.997, \, A_{VS} = 0.9735, \, = 409.1 k, R_O = 216.5 \Omega$

$= R_O \parallel$

# UNIT – II

# HIGH FREQUENCY AMPLIFIERS

# 1) GAIN IN DECIBELS.

The ratio of output voltage to inlput voltage is called voltage gain. The gain is expressed in logarithmic scale rather than a linear scale. The unit of this logarithmic scale is called decibel (dB).

$A_V = 2. Log ||$

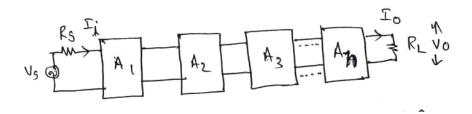

## 2) GAIN FOR N- STAGE CASECADED AMPLIFIER.

The voltage gain of cascaded amplifier of n- stages is given by

=

For any single stage in cascaded amplifier

=

# Gain in (dB)

+. .....

# **ADVANTAGES.**

1) Overall gain is sum of individual gains in (dB).

2) Representation of gain is convenient for small and large values

**Ex**:  $A_V (dB) = -140 dB$  is for  $A_V = 0,0000001$

3) In audio amplifier, output is measured in decibels hence logarithmic scale is better than linear scale.

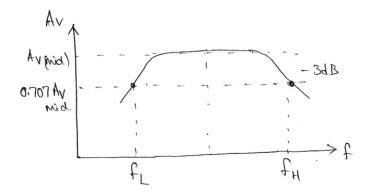

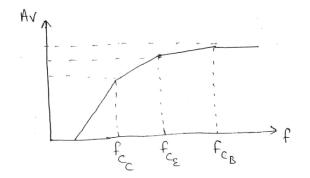

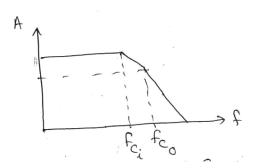

# 3) FREQUENCE RESPONSE.

1) The frequency response and bandwidth of the amplifier get affected due to the cascade connection. The bandwidth of cascaded amplifier is always less than that of the bandwidth of single stage amplifier.

# 2) LOWER 3Db FREQUENCY

1) Let us consider the lower 3dB frequency of n identical cascaded stages is  $f_L(n)$ . The gain at  $f_L(n)$ . frequency is 0.707 or -3dB of its original value.

=

=

Squaring both sides.

2= 2= = = -1 =  $F_{L} = Lower 3dB of a single stage$

= lower 3dB of a identical cascaded stages.

# 3) UPPER 3 Db frequency.

Let us consider the upper 3dB frequency of n identical stages is  $f_{H(n)}$  it is the frequency for which the overall gain falls to 3dB of its original value.

Gain of n stage cascaded amplifier.

=

=

=

Squaring both sides.

=

$F_{H(n)} = cutoff$  frequency of cascaded amplifier.

= cutoff frequency of single stage

N = no. stages.

## 3) BANDWIDTH

On cascading, is always greater then  $f_L$  and  $f_{H(n)}$  is always less than  $f_H$ . therefore bandwidth of multistage amplifier is always less than single stage amplifier.

$(B.W)_n < (B.W)_{single stage}$

5) FOR n non identical stages of amplifier.

= 1.1

# 6) EFFECT OF COUPLING CAPACITOR.

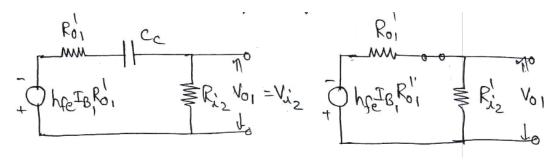

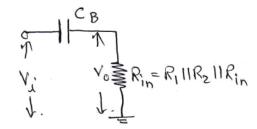

1) consider a two stage RC coupled amplifier.

2) Consider small signal model of first stage output and second stage input section.

## 3) VOLTAGE GAIN at mid frequency range.

At mid and high frequency capacitive reactance is very small hence replaced by short circuit.

$A_{Vmid} = =$

# 4) VOLTAGE GAIN FOR LOW FREQUENCY RANGE.

At low frequency the capacitive reactance is considerable value.

Hence taking coupling capacitor into account as shown in figure.

$$V_0 = -(h_{fe})$$

= -  $h_{fe}$

$$V_0 =$$

Dividing both sides by,

$\begin{array}{l} A_{V\;Low} \\ A_{V\;Low} = \\ = \\ = \\ At & f = n \\ & = 0.707 \\ At = 0 \\ , \\ = 1 \\ At = , \\ At = , \\ \end{array}$

At cutoff frequency  $f_L$  the fells to 3dB from  $A_{\nu Mid.}$  This frequency is also called as lower 3dB frequency fig.7

# 5) VOLTAGE GAIN for high frequency.

At high frequency the capacitors have low reactance hence act as short circuit, there fore the gain drops to zero beyond frequency  $f_{\rm H}$

At f=

At f =

## 6) the gain frequency response is given below.

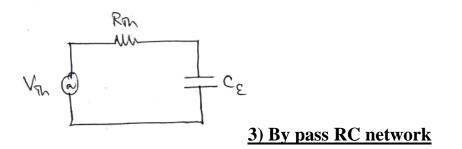

## 7]ANALYSIS OF EFECT OF COUPLING AND BYPASS CAPACITORS.

1) Consider a single stage amplifier.

2) h- parameter model.

Output voltage

$V_O = (-h_{fe} I_B) R_C$

Input voltage, Applying KVL to input loop.

- -- = 0 = = =,

# 3) Voltage gain.

$A_V = \; = \;$

$A_V =$

# 4) VOLTAGE GAIN FOR mid frequency.

All capacitors provide low reactance at mid and high frequencies, hence capacitance are neglected.

= =

# 5) VOLTAGE GAIN for low frequency.

At low frequency capacitive reactance are considered.

```

=

A<sub>V Low</sub> =

=

=

```

$$= = 0.707.$$

At f =,

The cutoff frequency or lower 3dB frequency is  $f_L$ , at this frequency gain falls to 0.707 from maximum.

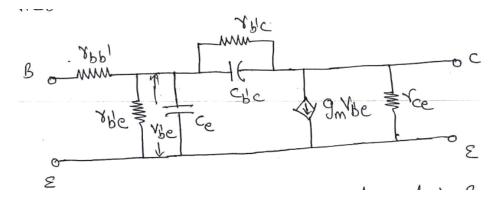

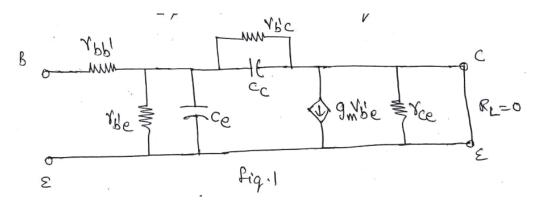

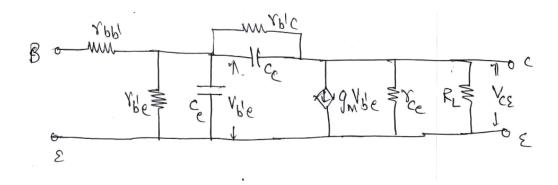

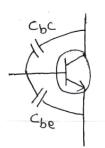

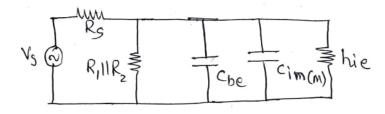

### 8) HYBRID-TT MODEL

1) At high frequencies. The h- parameter model is not suitable, because of change in transistor behavior.

i) The values of h- parameter are not constant at high frequencies.

ii) At high frequency h- parameters behavior is complex.

2) Hence the h-parameter model is replaced by HYBRID – TT model.

3) HYBRID – TT CE trans conductance model.

The parameters considered are independent of high frequency but dependent on quiescent operating point.

$Cb^1 e \rightarrow diffusion capacitance (C_e)$

$Cb^1c \rightarrow Transition capacitance (C_C)$

$r_{bb}^{1} \rightarrow$  The bulk resistance between external base terminal and internal node B<sup>1</sup> is represented as  $r_{bb}^{-1}$  (base spreading resistance.)

$r_b{}^1_e \rightarrow$  base emitter internal resistance.

$r_{b}{}^{1}_{C} \rightarrow$  the variation of voltage across the collector to emitter junction results in base-width modulation. The change in the effective base width causes the emitter current to change. This effect between output and input is taken into account by connecting  $r_{b}{}^{1}_{C}$  between collector and base.

$g_m \rightarrow Due$  to the small changes in voltage  $V_{b\,e}^{1}$  across the emitter junction, there is excers – minority carrier concentration injected into the base which is proportional to the  $V_{b\,e}^{1}$ . This results in small signal collector current, with collector shorted to the emitter is also proportional to the  $V_{b\,e}^{1}$ .

This effect accounts for the current generation  $g_m V_{be}^{1}$ .

$G_m = |constant|$

$\rightarrow$  The r<sub>ce</sub> is the output resistance.

# 9) TYPICAL VALUES.

$G_{m} = 50 \text{ mA/V}$   $R_{bb}^{1} = 100\Omega$   $r_{b}^{1}{}_{e} = 1k\Omega$   $r_{b}^{1}{}_{C} = 4M\Omega$   $r_{ce} = 80k\Omega$   $C_{b}^{1}{}_{e} = C_{e} = 100PF$   $C_{C} = 3 PF$

## 10] TRANSCONDUTANCE [gm]

1) consider a CE amplifier shown in fig.1

2) Consider the transistor in active region (amplifier)

### a) D.C conditions

$I_C = I_O$ .

$I_{\rm E}=I_{\rm C}$

$$I_E = I_C$$

$V_{CE} = V_{CC} - I_{C.}R_{C.}$

b) A.C condition.

Total collector current

[ Sum of a.c d.c current]

$I_{\rm C}=I_{\rm O}$

${}_{=}\,I_O$

$i_C = I_O$  .

$i_{\rm C} = I_{\rm c}$ .

$i_{\rm C}=I_{\rm c}$

$i_C = I_c +$

$I_C = d.c$  collector current

= a.c collector current.

Consider a.c component of collector current.

$i_C =$

$i_C = g_m$

Hence trans conductance is ratio of output current (I<sub>C</sub>) to input voltage

$G_m = =$

### NOTE:

1)  $g_m$  is slope of curve drawn between  $I_c$  and

[this model is valid for  $\langle V_T$ ]

2) The base current and the input resistance at the base

3) The emitter current and the input resistance at the emitter.

4) Relation between  $r_e$  and  $g_m$

5) Relation between and

6) Voltage gain of CE amplifier is given by

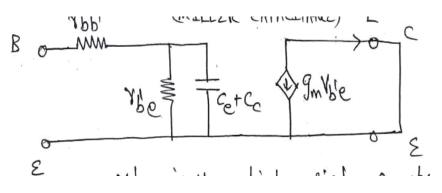

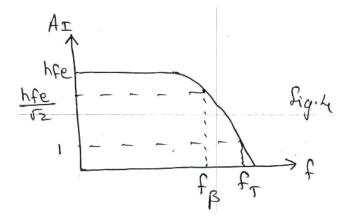

## 11] CE SHORT- CIRCUIT CURRENT GAIN.

1) Consider a single stage CE transistor amplifier with load resistor  $R_L$  short circuited fig.1

(MILLER CAPACITANCE) IL

rb<sup>1</sup>c is very hight resistance hence neglected

r<sub>ce</sub> is shunt to short circuit

$$Z = rb^1 e \parallel (-j)$$

Z =

Input voltage  $Vb^{1}e = .Z$

z =

Current gain of CE short circuit is given by

$A_I =$

$A_{I} = \; = \; = \; = \;$

The above equation indicates that current gain is dependent on frequency f.

At Low frequency A<sub>I</sub> -

At Low frequency current gain falls as shown in fig 4.

At f = , |  $A_I$ |=

# 12) FREQUENCY,,

# a) cutoff frequency .

The frequency at which gain of CE amplifier falls to 3dB or 0.707 from its maximum value is called ''

# **b) cutoff frequency**

The frequency at which gain of CB amplifier drops to 3dB or 0.707 from its maximum value is called '

At f =

# c) cutoff frequency fT

The frequency at which gain of CE short circuit amplifier becomes unity.

$\mathbf{F} =$

>>1

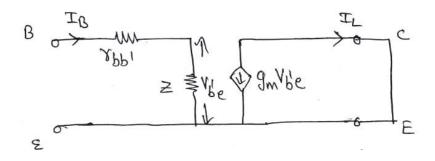

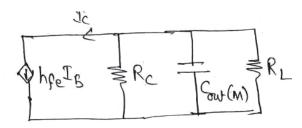

# 13) CURRENT GAIN OF CE AMPLIFIER WITH RESISTIVE LOAD

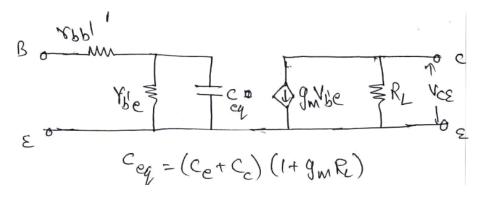

1) A CE amplifier with is shown below (hybrid)

Considering millers theorem.

$A_I = \ = \ =$

Gain and frequency response is shown below

# 14) GAIN BANDWIDTH PRODUCT

a) Gain bandwidth product for voltage

The product of gain and bandwidth is given by.

# **b) GAIN BANDWIDTH PRODUCT for current**

# **15) SINGLE STAGE CE AMPLIFIER RESPONSE**

## a) Low frequency analysis of BJT.

1) The capacitors, provide different reactance as frequency varies.

# 2) Input RC network.

The voltage

At f =

The cutoff frequency

2) Output RC network.

The cutoff frequency is given by

Phase angle

The cutoff frequency is given by

# 4) Hence each RC network has a cutoff frequency.

The RC network with higher cutoff frequency will be dominant network, which determines the over all gain. Beyond the frequency the gain drops at -20dB/dec

is highest hence capacitance is dominant pole.

40) b) high frequency analysis of BJT

1) The capacitors  $C_B$ ,  $C_c$ ,  $C_E$  acts as short circuit at high frequency. Therefore they do not affect the amplifier gain frequency response.

- 2) At high frequency, the internal stray capacitance effect the gain of amplifier.

- $\rightarrow$  Collector base junction (Transition capacitance)

- $\rightarrow$  Base emitter junction (diffusion capacitance)

3) Considering miller effect of capacitance for CE amplifier

$C_{in}(m) = C_{bc}(1+A_V)$

$C_{out}\left(m\right)\ = C_{bc}\ = C_{bc}$

#### **4) INPUT RC NETWORK**

The cutoff frequency

Phase angle

## 5) OUTPUT RC NETWORK

The cutoff frequency

$\mathbf{R} =$

C =

Phase angle

6) The response of circuit is decided by lower cutoff frequence out of the two frequencies , .

is lower than hence the input capacitance dominates the response of amplifier with change in frequency.

#### <u>ASSIGNMENT – I</u>

1) explain the importance of gain in decibel in decibel unit.

2) Explain the frequency response of amplifier at low and high frequencies.

3) In a single stage RC coupled CE amplifiers, expain the effect of by pass and coupling capacitor.

4) Explain BJT hybrid model.

5) derive expression for trans conductance  $g_m$ .

6) Prove that the hybrid model the diffusion capacitance is proparional to the emitter bias current.

7) Consider CE single stage with a resistive load  $R_L$ , using millers theorem find out input capacitance at mid band frequencies and high frequencies.

8) Explain how the parameters of hybrid model varying with  $I_E$ ,  $V_{CE}$  and temperature.

9) Derive the expression for CE short circuit current gain  $A_I$  as a function of frequency using hybrid model.

10) Derive the expression for CE amplifier current gain with resistive load.

- 11) Define, , and give relation between,

- 12) Explain low frequency response of CE amplifier.

- 13 Explain high frequency response of CE amplifier.

- 14) Derive expression for gain band width product

- 15) derive  $F_L$  and  $f_H$  for n stage cascade amplifier comment on bandwidth of cascaded amplifier.

#### ASSIGNMENT – 2

#### **GAIN**

1) for an amplifier, mid band gain 100 and lower cutoff frequency is 1KHZ. Find the gain of an amplifier at frequency 20hz.

#### Ans = 2

2) For an amplifier, 3dB gain is 200 and higher cutoff frequency is 20khz. Find the gain of am amplifier at frequency 100 Khz.

#### Ans = 115.47

3) determine the low frequency response of the amplifier shown below. Draw the frequency response.

Ans:

4) at  $I_C$  = 1MA and  $V_{CE}$  = 10V, a certain transistor data shows  $\,$  = 3PF,  $\,$  = 200 and  $w_T$  =-500 M rad/sec

Calculate  $g_m$ , = and

#### Ans (g<sub>m</sub> = 38.46 MA/V, , , = 2.5 M rad/sec)

5) Short circuit CE current gain of transistor is 25 at a frequency of 2Mhz. it = 200khz. Calculate

i) ii) A<sub>I</sub> at frequency of 10 Mhz and 100 MHZ

Ans (50 Mhz, = 250,  $A_I = 5$  and 0.5)

6) for a BJT amplifier, the following values one known.

Operating temperature  $T = 300^{\circ}$  k,  $I_{Ca} = 2MA$ ,  $r_{bb}^{-1} = 100 \Omega$ ,  $= 1000\Omega$ ,  $= 2M\Omega$ ,

$r_{ce} = 810 K\Omega$ ,  $f_T = 50 Mhz$ . obtain the h-parameter if  $K = 1.38 \text{ j/}^{\circ} k$  and  $q = 1.6 \ 10^{-19}$

#### Ans $(g_m = 77.23 \text{ A/V}, = 5 = 51.619)$

7) A BJT has following parameter measured at  $I_C = 1MA$ ,  $f_T = 4$  Mhz

Find , and  $r_{bb}{}^1$  for  $R_L$

## Ans $(g_m = 0.038 \text{ A/V}, r_{bb}^1 = 400 \Omega, f_H = 637.64 \text{ khz})$

8) Given the following transistor measurement made at  $I_C$ = 5MA,  $V_{CE}$  = 10V and at room temperature  $A_{Ie}$  = 10 at 10 MHz,  $C_e$  = 3PF.

Find  $C_e$ , , and  $r_{bb}^{1}$

Ans (C<sub>e</sub> = 304 PF,  $r_{bb}^{1} = 80 \Omega$ ,  $f_T = 100.05 mhz$ )

9) The amplifier shown in fig below uses a BJT with  $g_m = 0.2 \text{ A/V}$ ,  $C_e = 200 \text{ PF}$ ,  $r_{bb}^{-1} = 100 \text{ } \Omega$ ,  $C_c = 4 \text{PF}$ ,

Draw hybrid circuit and find  $A_{V(mid)}$ ,

Ans (-100,

parameters of the transistor used in the circuit of fig.below are  $g_m = 50$  m A/V,  $C_e = 100$  PF, ,  $r_{bb}{}^1 = 100 \Omega$ ,  $C_c = 3$ PF,

Find a) upper 3dB frequency of A<sub>I</sub>

b) The voltage gain A<sub>VS</sub>.

#### Ans $(f_H = 3.77 MHZ, A_{VS} = -50)$

11) For a single CE amplifier whose hybrid parameters are given below, what is half the value obtained with  $R_s = 0$ , Hybrid – parameter,  $g_m = 50 \text{ m A/V} r_{bb}^{-1} = 100\Omega$ ,  $C_c = 3PF$ ,  $C_e = 100PF$ .

#### Ans $(\mathbf{R}_{\mathrm{S}} = 122.2 \ \Omega)$

12) A single stage CE amplifier has upper 3dB frequency of voltage gain  $f_H = 4$  MHz, with a load resistance  $R_L = 600\Omega$  it the transistor parameter are  $g_m = 50$  m A/V,  $r_{bb}^{-1} = 100\Omega$ ,  $C_C = 3PF$   $f_T = 300$ mHz,  $h_{fe} = 100$ .

Find 1) The value of  $R_S$  which will result in the required value of  $f_H$ .

2) The mid band gain with above value of  $R_s$ . Ans (311.8 $\Omega$ , -24.88)

13) A high frequency amplifier uses a transistor which is driven from a source with  $R_s = 0$ . Calculate value of  $f_H$ , if  $R_L = 1K\Omega$ , Assume typical values of hybrid – parameters.

Ans (fH = 0.629 MHz) (fH = 1.545 MHz)

14) A high frequency amplifier uses a transistor which is driven from a source with  $R_S = 1K$ , calculate value of  $f_H$ ,  $A_{V(Low)}$ ,  $A_{V(High)}$ , it  $R_L = 0$ ,  $R_L = 1K\Omega$ , consider typical values of hybrid – parameters.

#### Ans (2.95 MHz, fH = 1.2 MHz, AV(Low) = -23.8)

#### **GAIN BRAMDWIDTH PRODUCT**

15) If tour identical amplifiers are cascaded each having  $f_L=10mHz$  determine the overall lower 3dB frequency  $f_L$ .

#### Ans (229.9Hz)

16) if foure identical amplifiers are cascaded each having  $f_H = 100$ KHz, determine the over all upper 3dB frequency  $f_H$ .

#### Ans (43.5 kHz)

17) Three identical non – interacting amplifier stages in cascade have an overall gain of 1dB down at 30 Hz compared to midband. Calculate the lower cutoff frequency of the individual stages.

#### Ans (FLn = 15.23 Hz , fL = 7.782 Hz)

18) if the overall lower and higher cutoff frequencies of a two identical amplifier cascade are 600Hz and 18KHz respectively, compute the value of the individual cutoff frequencies of both the amplifier stages.

Ans (FH = 27.97 KHz , fL =386 Hz)

# **MOS AMPLIFIERS**

#### **Basic concepts**

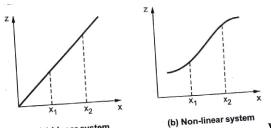

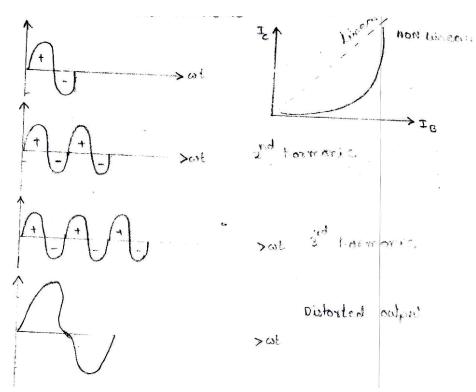

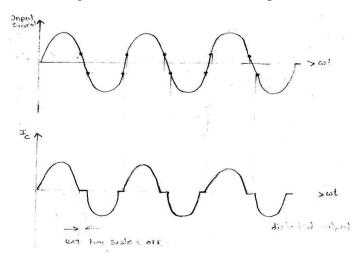

Usually the input-output characteristics of an amplifier are non- linear. It can be approximated by a polynomial over some signal range:

For the narrow range of x the polynomial can be approximated to

Where : represents the operating point

= Represents the small signal gain

(a) Linear system (b) Non-linear system When > x(t) we have This indicates the linear telationship between the input and output. The fig.4.1.1 (a) and 4.11 (b) shows the input – output characteristic of a linear and non – linear systems

In the design of a high performance amplifier the trade- off between noise. Linearity gain, bandwidth, supply voltage, power dissipation, input/ output impedance, speed and voltage swings impose many challenges. This is illustrated by the analog design octagon shown in fig. 4.1.1

Noise Linearity

Gain

Speed

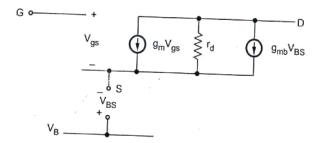

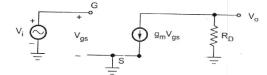

#### MOS small signal model

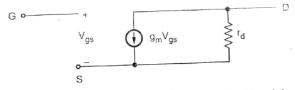

The fig shows the MOS small signal low frequency model. We know that the drain current is a function of the gate- source voltage. This is represented by a voltage dependent current source  $g_m$   $V_{gs}$  in the model. The resistance between D and S is represented by  $r_o$ . it is the change in drain current due to the change in drain source voltage and it is given by

The drain current also changes due to a change in the back gate bias. This dependence is represented by another current source  $V_{bs}$  connected between D and S. in saturation  $g_{mb}$  can be given by

Neglecting the body effect the MOS small signal low frequency model is as shown in the fig

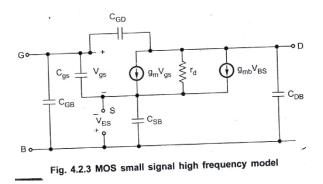

At the frequency, device capacitances have their own significance and they are represented in the model as shown in the fig.

Fig. 4.2.2 MOS small signal low frequency model

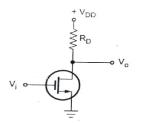

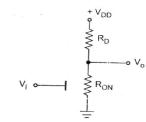

#### Common source amplifier with resistive load

The fig shows a common source stage of MOSFET amplifier. Here, the variations in the gatesource voltage produce variations in the drain current. This current passes through a drain resistance ( $R_D$ ) to generate an output voltage.

#### **Operation**

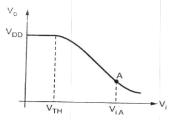

When  $V_i = 0$ , MOSFET is OFF and  $V_0 = V_{DD}$ . As  $V_i$  increases from zero and approaches  $V_{TH}$ , MOSFET start to turn on. Due to this, drain current  $I_D$  starts flowing through  $R_D$  reducing  $V_o$ . as we go on increasing  $V_i$  and if  $V_{DD}$  is not excessively low,  $M_1$  goes in saturation. In saturation  $V_o$ is given by,

(a) Common source stage

(b) Input-output characteristics

(c) MOS small signal model for the saturation region

(d) Equivalent circuit in deep triode region

If we further increase  $V_i$ ,  $V_o$  drops more and the MOSFET continues to operate in saturation until  $V_I$  exceeds  $V_o$  by  $V_{TH}$  as indicated by point A in the fig At point A, we have

In the triode region,  $V_{\rm i} > V_{\rm iA}$  and  $V_{\rm o}$  is given by

If  $V_i$  is large enough to drive MOSFET into deep triode region, <<2 and from the equivalent circuit (See fig ) we have

Voltage gain

Since itself varies with the input signal and it is given by

The equation (4.3.4) indicates that the gain of the circuit varies significantly with the signal swing if input signal  $(V_i)$  is large and in this case circuit operates in a large signal mode. The dependence of the gain upon the signal level leads to nonlinearity and this is nor desirable.

Maximizing voltage gain

We have

From equation (4.3.5) we can observed that, magnitude of  $A_V$  can be increased by increasing W/L or  $V_{RD}$  or decreasing  $I_D$  if other parameters are constant.

Trade off

- There is limitations on increasing device size, since larger device size leads to greater device capacitances.

- Higher V<sub>RD</sub> limits the maximum voltage swings.

• Higher value of R<sub>D</sub> increases output time constant and makes channel length modulation effect significant.

Thus more is a trade – off between gain, bandwidth and voltages swings.

Including effect of channel length modulation the voltage gain is given by

Using

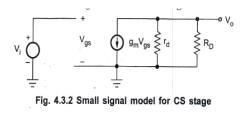

The fig shows the small signal model for CS stage.

From the fig we have,

$$V_o = g_m V_{gs}$$

The expression for  $A_V$  in equation 10 and 9 are same, however, later one if easy to derive.

# UNIT-III FEEDBACK AMPLIFIERS

## 1) Feed back

feed back is a process in which part of outputn(i.e.faction) is fed back to input signal.

feedback improves performance of amplifier by reducing noise and distorstion and maintains stability.

## 2) Types of feedback

There are two types of feedback

i) Positive feedback

ii) Negative feed back

## i) Positive feed back

When the input signal and part of output signal are in phase the feedback is called positive feedback.

$V_i = V_s + V_f$

## ii) Negative feed back

When the input signal and part of output signal (feedback signal) are out of phase, the feedback is called negative feedback.

$V_i = V_s + (-V_f)$

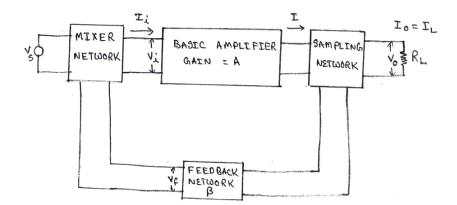

## 3) Feedback concept

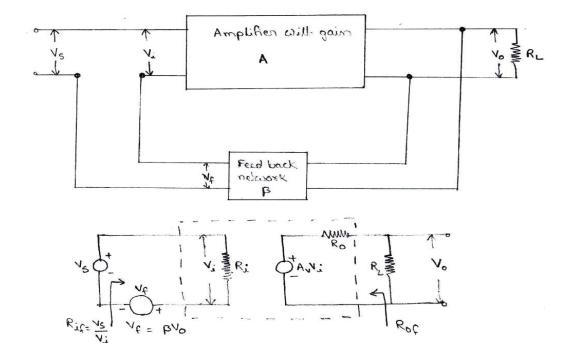

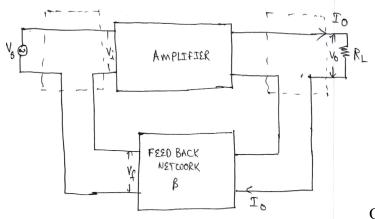

The output voltage or current by means of a sampling network is applied to input through a feedback two part network, as shown fig.1

At the input the feedback signal is combined with the input signal through a mixer network and is feed back into the amplifier.

#### i) Sampling network:

There are two ways to sample the output voltage or current. The output voltage is sampled by connecting the feedback network in shunt across the output. The output current is sampled by connecting the feedback network in series across the output.

#### ii) Feedback network:

If may consists of resistors, inductors, capacitor or only resistive components. it provides reduced portion of the output as feedback signal to the input mixer network.

$V_{\rm f} = V_{\rm o}$

factor (lies between '0' and '1')

#### iii) Mixer network:

Like sampling there are two ways of mixing feedback signal with input signal.

There are two methods

1) Series input

2) Shunt input

## 4) Gain of feedback amplifier

An amplifier with feedback is considered

Let gain of amplifier without feedback = A = Let gain of amplifier with feedback =  $A_f$ Let input voltage without feedback =  $V_s$ Let output voltage without feedback =  $V_o$ Let the feedback voltage be = 'V<sub>f</sub>' But 'V<sub>f</sub>' is fraction of output voltage

Feedback factor Considering negative feedback Input signal with feedback

Gain of amplifier with feedback

Divide both denominators is & numerator with

For positive feed back

Gain with feedback

is positive if, the feed back is turned as negative feed back or degenerative feedback.

is negative if the feedback is tunned as positive feed back or regenerative feed back.

#### 5) Sensitivity

The charge in the gain with feedback is less than the change in gain without feed back by the factor (1 + A).

The fraction change in amplification with feedback divided by the fractional change without feedback is called SENSITIVITY of the transfer gain.

## 6) De sensitivity

The reciprocal of the sensitivity is called the de sensitivity.

D = 1 +

is called loop gain

## 7) Frequency response and bandwidth

The gain of amplifier with negative feedback is given by

$\rightarrow$  Response at lower cutoff frequency with feed back

cut off frequency without feedback.

Hence from above expression, it is clear that lower cutoff frequency with feedback is less than lower cutoff frequency without feedback a factor (1 + ).

$\rightarrow$  Therefore by introducing negative feedback low frequency response of the amplifier is improved.

$\rightarrow$  Response at higher cutoff frequency with feedback

Hence from above expression it is clear that upper cutoff frequency with feedback is greater than higher cutoff frequency without feedback by factor (1 + ).

$\rightarrow$  Therefore by introducing negative feedback high frequency response of the amplifier is improved.

$\rightarrow$  Band width of the amplifier.

B. = Upper cutoff frequency - lower cutoff frequency.

B. =

Hence from above expression it is clear that bandwidth of a amplifier increases by introducing negative feedback.

## 8) Frequency distortion

The feedback network may consist of R, l, C components if the feedback network does not contain reactive elements, the overall gain is not a function of frequency under such conditions frequency and phase distortion is substantially reduced.

if reactive components are present in feedback network, the reactance's or these components will change with frequency changing ... As a result gain also changes with frequency.

## 9) Non linear distortion and noise

Consider a large amplitude signal applied to a stage of an amplifier so that the operations of an active device (i.e, transistor) extend slightly beyond its range of linear operation. As a result of this the output signal is slightly distorted. Now if a negative feedback is introduced to the amplifier stage the voltage gain reduces. But if the input signal is increased by the same amount by which the gain is reduced, the output signal amplitude remains the same (i.e it was without feedback) considering distorting in both cases the distorting is reduced by employing negative feedback

is distortion without feedback.

#### $\rightarrow \underline{NOISE}$

it has been observed that there are many sources of noise in an amplifier depending upon the active device used in the circuit. It will be interesting to know that with the use of feedback the magnitude of noise (N) is reduces by a factor of (

N = noise without feedback

## 10) Stabilization of gain

The gain with negative feedback of amplifier

On differentiation with respect 'A'

fractional change in amplifier voltage with feedback.

fractional change in amplifier voltage with out feedback.

'sensitivity' it indicates ratio of percentage change in voltage gain with feedback to the percentage change in voltage gain without feedback.

'de sensitivity' it indicates the factor by which the voltage gain has been reduced due to feedback.

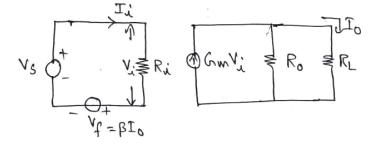

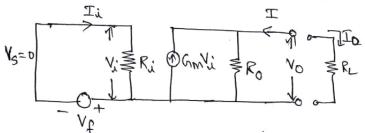

#### A. voltage – series feedback connection

1. The block diagram of a voltage series feedback is shown in fig. Below.

2) The input to the feedback network is in parallel with the output of the amplifier. A fraction of the output voltage through the feedback network is applied in series with input voltage of the amplifier.

3) The shunt connection at the input increases the input resistance

4) The amplifier in this case is a true voltage amplifier the voltage feedback factor is given by

# Input resistance

Considering input loop in fig 2.

By using KVL

Hence input resistance with feedback increases by factor than input resistance () without feedback.

Output resistance

For determining output resistance,

is disconnected and V<sub>s</sub> is set to zero.

A external voltage 'V' is applied across the output terminals and the current I delivered by 'V' is calculated.

By applying KVL to output loop

V = A + I

Hence, output resistance with feedback decreases by (1+) than output resistance without feedback.

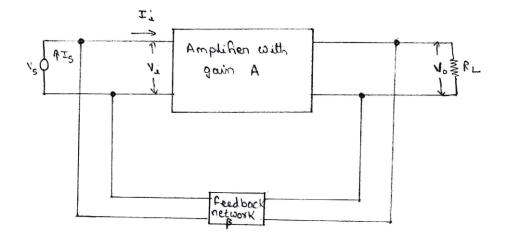

#### **B.** Voltage shunt feedback

1) A voltage shunt feedback block diagram is shown below in fig.1

2) The fraction of the output voltage is supplied in parallel to input voltage through the feedback network.

3) The feedback signal is proportional to the output voltage.

Feedback factor

This type of amplifier is called a trams resistance amplifier.

4) The voltage shunt feedback provides a stabilized overall gain and decreases both input resistance by a factor

The voltage shunt feedback topology is shown below.

The amplifier input circuit is represented by Norton's equivalent circuit and output circuit is represented by terminals equivalent.

KCL at input node

Output voltage is given as.

= open circuit trans resistance without feedback

trans resistance without feedback taking load resistance using in eq(1)

#### **Input resistance**

with feedback is given by

## **Output resistance**

The output resistance is calculated by open

circuiting input source and eliminating at output.

KVL to output loop

Input current

Using in eq (1)

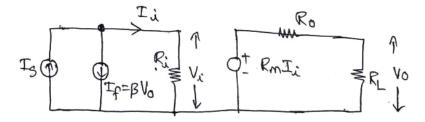

#### C) Current series feedback

1) The block diagram of a current series feedback is shown below

2) In current series feedback, a voltage is developed which is proportional to the output current.

3) Because of the series connection at the input and output the input and output resistance get increased. This type of amplifier is called trans conductance amplifier.

4) The feedback factor is given by

5) Input resistance

Output resistance

The current series feedback topology is shown below.

The amplifier input circuit is represented by Theremins equivalent circuit and output circuit by Norton's equivalent circuit.

KVL to input loop

Output loop

= Trans conductance without feedback.

trans conductance without feedback taking .

## **Input resistance**

Using value in eq(1)

## **Output resistance**

$v_{\pm}^{\varphi}$  The output resistance can be calculated by short circuiting input source and without at output circuit.

KCL at output node

Input loop

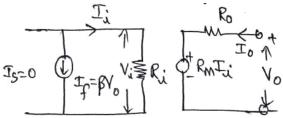

#### **D)** Current shunt feedback

1) A current shunt feedback topology is shown below

2) It is called series derived shunt fed feedback system.

3) in this type of feedback connection, the input resistance is reduced and output resistance is increased.

4) this is a current amplifier.

5) The feedback factor

Input resistance

Output resistance

The current shunt feedback topology is shown below

The amplifier input and output is replaced by Norton's equivalent circuit.

#### KCL at input node

Output current

,

Using in eq (1)

## Input resistance

# **Output resistance:**

The output resistance is calculated by open circuiting the input source and is removed.

#### KCL at output node

Input node

[

Using in eq (1)

## **15) CLASSIFICATION OF AMPLIFIERS.**

The amplifiers can be classified into four types.

- Voltage amplifier.

- Current amplifier.

- Trans conductance amplifier.

- Trans resistance amplifier.

### 1) Voltage amplifier

If the amplifier input resistance is large compared with the source resistance then. If the external load resistance is large compared with the output resistance of the amplifier, then.. Such amplifier circuit provides a voltage output proportional to the voltage input, the proportionality factor does not depend on magnitude of the source and load resistance.

Hence this amplifier is called VOLTAGE amplifier. Ideal voltage amplifier has infinite input resistance and zero output resistance

Practical voltage amplifier has

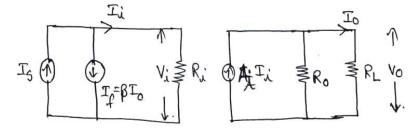

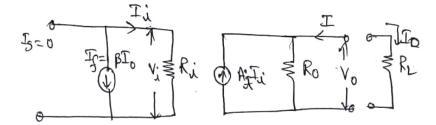

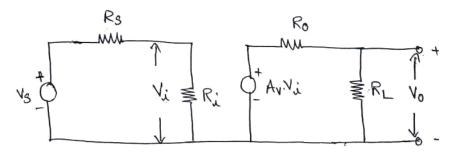

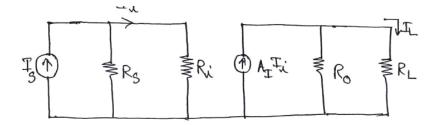

#### Equivalent circuit of voltage amplifier

#### 2) Current amplifier.

If amplifier input resistance is zero then input current is equal to source current if amplifier output resistance is infinity, then such amplifier provides a current output proportional to the signal input current and the proportionality factor is independent of source and load resistance. This amplifier is called current amplifier.

Ideal current amplifier has = 0, =

Practical current amplifier has << , >>

#### Equivalent circuit of current amplifier.

#### 3)Trans conductance amplifier

In this amplifier, an output current is proportional to the input voltage and the proportionality factor is independent of the magnitudes of the source and load resistance.

Ideally this amplifier has =, =

Practical this amplifier has >>, >>

Equivalent circuit of Trans conductance amplifier

#### **4)Trans resistance amplifier**

In this amplifier an output voltage is proportional to the input signal current and the proportionality factor is independent of the source and load resistance.

Ideally this amplifier must have zero input resistance and zero output resistance .

Practically << and <<

#### Equivalent circuit of trans resistance amplifier

## 16) Analysis of feedback amplifier [identifying topology]

**<u>STEP 1</u>** identifies topology.

• Sampling network.

a) by shorting the output  $V_o = 0$ , if feedback signal ( $V_f$ ) becomes zero then it is voltage sampling.

b) by opening the output loop i.e. = 0, if feedback signal I<sub>f</sub> becomes zero then it is current sampling

• Mixing network.

a) if the feedback signal is subtracted from the externally applied signal as a voltage in the input loop, then it is series mixing.

b) if the feedback signal is subtracted from the externally applied signal as a current in the input loop, then it is shunt mixing.

**<u>STEP (2)</u>** : finding input circuit

- For voltage sampling make  $V_0 = 0$  by shorting the output.

- For current sampling make  $I_o = 0$  by opening the output loop.

Step (3) : finding output circuit

- For series mixing make  $I_i = 0$  by opening the input loop.

- For shunt mixing make  $V_i = 0$  by shorting the input.

Step 4): Draw the h-parameter model. For given circuit.

Step(5): Find gain 'A'

Step (6): find feedback factor '

**Step (7):** find all parameters.

#### 7) Voltage series feedback:

A emitter follower circuit is example of voltage series feedback.

The voltage across  $R_E$  resistor is output voltage, simultaneously  $R_E$  resistor voltage is considered for input loop also.

Here, in this circuit is feedback factor is unity.

- Output voltage

- KVL to input loop

3) If output port is short circuited then feedback signal becomes zero. There voltage sampling is done here.

As the feedback signal '' is subtracted from input signal, their input mixing is series.

Therefore the feedback used in this circuit is voltage series feedback.

4) For finding input and output circuit and a.c analysis the circuit is rearranged.

For input circuit

As output sampling is voltage, make output  $V_{\rm o}$  = 0.

Then input loop is.

For output circuit,

Now, making input current , , so  $R_E$  appears only in output circuit as shown above.

### 5) A.C analysis

## 6) Open loop voltage gain:

Feedback factor

De sensitivity D = 1 +

## 1) Open loop voltage gain

## 2) Feedback

# 3) De sensitivity

D = 1+

4) Voltage gain

# 5) Input resistance

$= 1000 + 1100 = 2100 \ \Omega$

## 6) Output resistance

#### 18) Voltage shunt feedback

A collector base bias circuit is example of voltage

shunt feedback. The circuit is shown below.

1) By short circuiting the output,  $V_0$  becomes zero hence feedback current  $I_f$  becomes zero. Hence it is voltage sampling. As the feedback current is given to input the mixing network is shunt network. The topology is called voltage shunt feedback.

Using miller's theorem is rearranged at input and output as R1 and R2

To find input circuit set  $V_0 = 0$ , then is connected at base and emitter. To find output circuit, set = 0, then is connected between collector and emitter.

We have

Input resistance

Find

D = 1+

= 2.854

# **19) Current series feedback**

1) The common emitter circuit with un by passed is example of current series feedback.

2) A. CE amplifier is shown below.

3) The  $R_E$  resistor is common to both input and output loop. Therefore voltage across  $R_E$  is considered as feedback voltage.  $V_F$

Hence output current  $I_o =$  is sampled and it is converted to voltage by feedback network.

Now, feedback back voltage is subtracted from to produce. Hence the circuit uses current series feedback.

### 4) Input and output circuit

In absence of output current ( then  $R_E$  belongs only to input when, then belongs to output circuit. Therefore  $R_E$  appears in input and output loop. The modified circuit is shown in below.

## 5) Open loop transfer gain.

Feedback factor

6) Find

[Take the values from ckt.]

1) De sensitivity D = 1 +

= -1.72

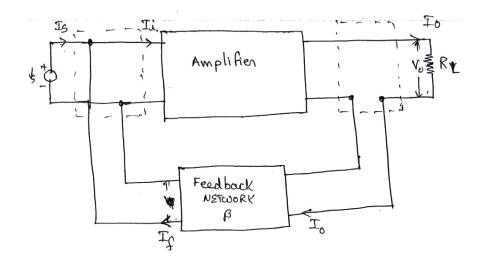

### 20) Current shunt feedback.

1) A CE amplifier in cascade mode with feedback can be considered as example of current shunt feedback.

2) Two stage cascaded with feedback

CE amplifier is shown below.

3) The feedback network consists of  $R_F$  and the output current = - = - is divided by the two resistors and feedback current is subtracted from and given to . Hence this configuration is current shunt feedback.

4.Input and output circuit.

As the resistor is connected to input and output of  $Q_1$  and transistor respectively. This resistor is replaced in shunt between base and emitter of by making

Similarly making is in parallel to of transistor.

The modified circuit is shown below.

## 4) Open circuit transfer gain

5) Find

,

,

[take the values from ckt.]

1) De sensitivity D = 1 +

= 0.394 K

# **OSCILLATORS**

## 1) OSCILLATOR

An oscillator is a circuit which generates an a.c signal without a.c input. An oscillator is a signal generator if produces a signal of constant amplitude and constant frequency.

### 2) Classification of oscillators.

The oscillators are classified based nature of signal, frequency and components, applications.

a) Based on wave forms

b) Relaxation oscillators.

c) Based on feedback

c) Based on frequency generated..

Audio frequency OSC [ upto 20 KHz]

Radio frequency OSC [ 20 KHz to 30 KHz]

Very High frequency OSC [ 30 MHz to 300MHz]

ULTRA HIGH frequency OSC [300MHZ to 3GHz]

MICRO WAVE frequency OSC.[ above 3 GHz]

e) Based on components

LC oscillators

RC phase shift oscillators

#### 3) Conditions for oscillations.

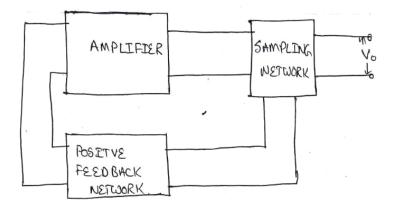

1) The oscillator circuit positive feedback. In order to produce oscillations the circuit must satisfy BARHAUSEN criterion. The black diagram of oscillator circuit is shown below.

#### **Block Diagram of Oscillator**

#### 2) Barkhausen criterion

The essential conditions for maintaining oscillations are.

i) |A| = 1, magnitude of loop gain should be unity.

ii) The total phase short of feedback signal should be  $0^0$  or  $360^0$

3) The condition that loop gain ) |A| = 1 gives a single and precise values of ) A, which should be set throughout the operation of the oscillator circuit, but in practice as transistor character tics and performance of other circuit components change with time, |A| will becomes greater or lesser than unity

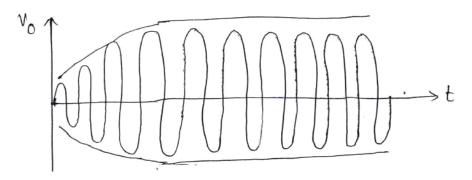

4) Hence in all practical circuits |A| should be set greater than unity so that the amplitude of oscillations will continue to increase without limit.

#### Sustained oscillations

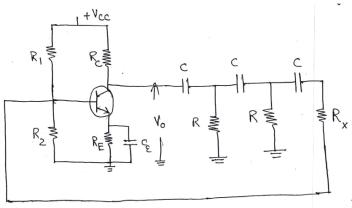

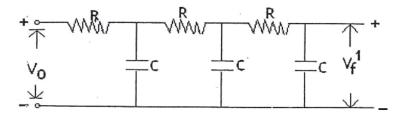

### 4) RC- phase shift oscillator

1) The Rc – phase shift oscillator are used in low frequency applications. The feedback circuit consists of resistors and capacitors.

below in fig.1

2) A RC phase shift oscillator is shown

3) The circuit consists of CE amplifier with three RC network connected to the feedback path. The feedback used in this circuit is voltage shunt feedback.

4) In order to generate sustained oscillations, the loop gain  $A \ge 1$  and phase shift of feedback signal must be  $0^0$  or  $360^0$  [BARKHAUSEN criteria]

### 5) Operation:

a) The oscillator circuit is not given any input signal. The output signal  $V_0$  is given to the feedback network. The feedback circuit takes fraction of output gives to input through resistor  $R_X$ . the feedback signal  $I_F$  is input to oscillator circuit. This signal is amplified again and again until loop gain A is equal to or greater than unity. Once sustained oscillations are developed.

b) The phase shift is provided by RC network. Each RC network introduces a phase shift of  $60^{\circ}$  and in total three RC network provide  $180^{\circ}$

The CE amplifier introduces  $-180^{\circ}$  phase shift and RC feedback network introduces  $180^{\circ}$  phase shift hence total phase shift of feedback signal is  $0^{\circ}$  or  $360^{\circ}$

c) As the Barkhausen criteria is satisfied, now the circuit produces sustained oscillations the output is a sinusoidal signal with constant amplitude and frequency.

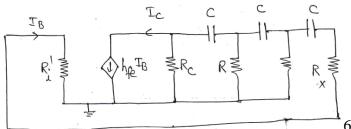

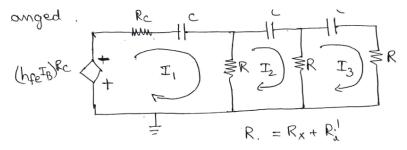

6) The frequency of oscillator is determined by the feedback network. The h-parameter equivalent circuit model is shown below.

The resistor  $R_X$  is in series with the circuit is re arranged.

KVL to loop (1)

\_

KVL to loop (2)

KVL to loop (3)

Using 3 equations find and (Cramer's rule).

=

I<sub>3</sub> = output current or feedback current = On solving above equation, the loop gain is obtained as

### Where

To have  $0^0$  as phase angle of feedback signal the imaginary part is made zero.

Solving for The frequency of oscillator is given by

Now, the loop gain is unity

|A| = 1

Consider real part and equate to unity

The minimum value of must bet 44.54

Hence by changing capacitor and resistors desired frequency of oscillations can be produced.

### 7) Advantages

- Simple in design

- Complete audio frequency range is covered.

- Produces sinusoidal output

- Fixed frequency oscillator.

#### 8) Disadvantages

- If frequency has to be altered all capacitors must be changed to same value.

- Frequency stability is poor.

5) Wien – bridge oscillator

- The weign bridge oscillator is a phase shift oscillator used for low frequency applications. The frequency of oscillator can be varied from 10 HZ ti 1MHZ.

- Weight bridge oscillator circuit is shown below.

- The circuit consists of a two stage RC coupled amplifier which provides a phase shift of  $360^{\circ}$  or  $0^{\circ}$ . A balanced bridge network used as shown in fig. the feedback is provided by bridge network and no need for any additional phase shift in feedback circuit.

- In order to generate oscillations the loop gain A should be greater than or equal to unity and phase angle of feedback signal should be  $0^0$  or  $360^0$  (Barkhausen rule)

- Operation

a) The oscillator circuit is not provided any input signal the output signal  $V_0$  is given to the feedback network (bridge circuit) the feedback circuit takes fraction of output and gives it to input i.e voltage across  $R_2$  and  $C_2$  parallel branch. This is obtained by voltage division rule.

b) Now, the amplifier has feedback voltage  $V_f$  as input and this signal is amplified again and again in the loop, At certain point the loop gain of amplifier becomes unity or greater than unity and sustained oscillations are developed.

c) Once Barkhausen condition is satisfied. Sustained oscillations are obtained. The desired frequency can be obtained by varying the capacitor values. By using common shaft both capacitors can be varied simultaneously.

d) By using wien-Bridge feedback network the oscillator becomes sensitive to a signal of only one particular frequency. Hence good frequency stability is obtained.

e) The frequency of oscillator circuit is given by

### **<u>6) Expression for frequency</u>**

The feedback voltage

Feedback factor

On solving above equation

To have zero phase shift of feedback network, imaginary part must be zero.

Let = = R, = C

Consider feedback factor '

Consider loop gain  $|A| \ge 3$ .

In order produce sustained oscillation the gain of amplifier should be greater than or equal to 3.

#### **LC oscillators**

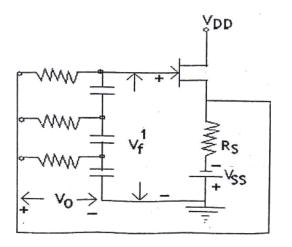

#### 6) Hartley oscillator

1) The LC oscillator use inductor and capacitor (tank circuit) for producing oscillations. These oscillators are used for high frequency range from 200 KHz up to few GHz.

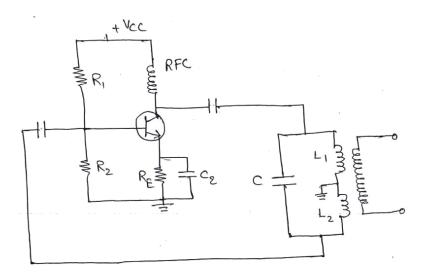

2) A Hartley oscillator circuit is shown below.

3) The circuit consists of CE amplifier with a LC tank circuit connected to output of amplifier. A coil called RFC (radiofrequency choke) is connected between the collector and  $V_{cc}$  supply

4) The feedback circuit consists of a tank circuit .it consists of two inductors  $L_1$  and  $L_2$  the inductor  $L_1$  is inductively coupled to coil  $L_2$  and the combination works as an auto transformer. A capacitor 'C' is connected in shunt with inductors  $L_1$  and  $L_2$

5) In order to generate oscillations, the loop gain A should be greater than or equal to unity. The phase angle of feedback signal should be  $0^0$  or  $360^0$  [Barkhausen rule]

### 6) Operation

a) The output of amplifier is taken at collector and given to feedback network. The feedback network (LC) takes fraction of output and gives to input hence the oscillator has feedback voltage  $V_f$  as input  $V_i$ . this signal is amplified again and again at certain point the loop gain becomes unity or greater than unit by which oscillations are developed.

b) The CE amplifier introduces  $180^{\circ}$  phase shift and the feedback network introduces a phase shift of  $180^{\circ}$ .

Hence total phase shift is  $360^{\circ}$  or  $0^{\circ}$

c) As conditions for oscillations are satisfied (barkhusen criteria) now sustained oscillations are produced.

d) The transistor should be for oscillation to start.

e) When the circuit is energized by switching on the supply, the collector current flows, then oscillations are produces be caused of positive feedback from the tank circuit.

f) The frequency of oscillations are given by

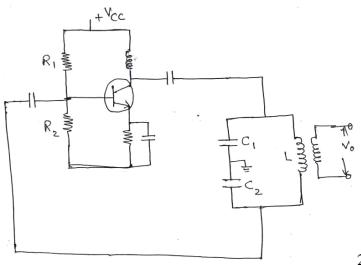

### 7) Colpitt's oscillator

1) The LC oscillators use inductor and capacitors (tank circuit) for producing oscillations. These oscillators are used for high frequency range from 200 KHz to few GHz.

below.

2) A colpitts oscillator circuit is shown

3) The circuit consist of CE amplifier with a LC tank circuit connected to output of amplifier. A coil called RFC (Radio frequency choke) is connected between the collector and  $V_{cc}$  supply.

4) The feedback circuit consists of a tank circuit. It has two capacitors  $C_1$  and  $C_2$  and a inductor L in shunt with capacitors. The output is taken at secondary of coupled coil with inductor L

5) In order to generate oscillations the loop gain A should be greater than or equal to unity. The phase angle of feedback signal should be  $0^0$  or  $360^0$  [Barkhausen Criteria].

### 6) Operation

a) The output of amplifier is taken at collector and given to feed back network. The feedback network (LC) takes fraction signal acts as input to amplifier. This signal is amplified again and again, at certain point the loop gain becomes unity or greater than unity by which oscillations are developed.

b) The CE amplifier introduces  $180^{\circ}$  phase shift and the feedback network introduces a phase shift of  $180^{\circ}$ .hence total phase shift is  $0^{\circ}$  or  $360^{\circ}$  hence the feedback is positive.

c) As conditions for oscillations are satisfied (Barkhausen criteria) now sustained oscillations are produced.

d) The transistor =, for oscillation to start.

e) When the circuit is energized by switching on the power supply, the collector current flows. Then oscillator is produced because of positive feedback from the tank circuit.

f) The frequency of oscillations are given by

### 7) Expression for frequency of oscillations

## **[HARTLEY & COLPITTS]**

Consider the following feedback amplifier circuit

The feedback voltage is given by

Feedback factor =

As phase of feedback network is  $180^{\circ}$

Consider therein equation circuit of amplifier

Gain of amplifier

Consider equation (1) and multiply both sides by A. According to Barkhausen criteria -A=1, for oscillations

This is required Loop gain, substituting value.

Are purely reactive elements

To have  $180^{\circ}$  phase shift the imaginary part of the denominator must be zero.

i.e.

According to the Barkhausen criterion must be positive and greater than or equal to unity. As is positive is positive, then will be positive only when and will have same sign. That is and must be of same type of reactance either both inductive or capacitive.

- $\rightarrow$  if are inductive then is capacitive then circuit is Hartley oscillator

- $\rightarrow$  if are inductive then is indicative then circuit is colpitts oscillator.

- a) For Hartley oscillator, frequency is obtained by.

b) For colpitts oscillator the frequency is obtained by

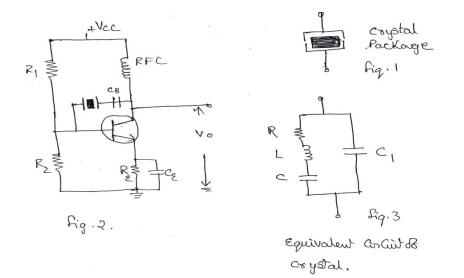

### 8) Crystal oscillator

- The crystal oscillator is basically a tuned oscillator. The crystal oscillator uses a piezo electric crystal as a resonant tank circuit.

- The crystal is usually made of quartz material and provides a high degree of frequency stability and accuracy.

- A slab is mounted between two metal plates and housed in a package which is equal to the size of postal stamp. The package as a whole is known as crystal and its symbol is shown in fig.1

- When a crystal is placed across an a.c source its starts vibrating. The amount of vibrations depends upon the frequency of applied voltage.

- A crystal oscillator circuit is shown in fig.2. A crystal is connected as a series element in the feedback path from collector to the base.

- The circuit frequency of oscillations is set by the series resonant frequency of the crystal equivalent circuit shown in fig.3

- The frequency of crystal oscillator is given by

- The changes in supply voltage transistor device parameters have no effect on the circuit operating frequency, which is held stabilized by the crystal.

#### 9) Frequency stability of oscillator

- The frequency stability of an oscillator is a measure of its ability to maintain the required frequency as precisely as possible over a long time interval as possible.

- The accuracy of frequency calibration required may be anywhere between  $10^{-2}$  and  $10^{-10}$

- The main draw back in transistor oscillator is that the frequency of oscillation is not stable during a long time of operation. The following are the factors which contribute to the change in frequency.

a) due to change in temperature the values of the frequency determining components viz resistor, inductor and capacitor will change.

b) Due to variation in the power supply unstable transistor parameters change in climatic conditions and aging.

c) The effective resistance of the tank circuit is changed when the load is connected.

• Due to variation in biasing conditions and loading conditions.

The variations of frequency with temperature is given by

Where , are the desired frequency of oscillation and the operating temperature respectively.

• As PIEZO ELECTRIC crystal have high Q values of the order of  $10^5$  they can be used as parallel resonant circuit in oscillators to get very high frequency stability of 1 ppm.

#### ASSIGNMENT - I

- Define oscillators how are oscillators classified ?

- What type of feedback is employed in oscillators? What are the advantages? Discuss the condition for sustained oscillations.

- What is Barkhausen criteria? Explain.

- Explain Hartley oscillator and derive the expression for frequency.

- Explain eoLLPIS oscillators and derive the expression for frequency

- Draw the circuit diagram of a Rc phase shift oscillator using BJT. Derive the expression for frequency of oscillation of RC phase shift oscillator using BJT.

- Explain the principle of operation of a weign bridge oscillator with the help of a neat diagram obtain an expression for its frequency of oscillations.

Show that the gain of weign bridge oscillator using BJT amplifier must be at least 3 for the oscillations to occur.

- What is piezo electric effect? Explain the working of crystal oscillator?

- What is the range of frequency over which a crystal oscillator may be normally used and why?

- What are the advantages and limitations of a crystal oscillator?

- Explain briefly about frequency and amplitude stability of oscillators.

# ASSIGNMENT -2

1) in Hartley oscillator, calculate  $L_2$  IF  $L_1 = 15$  mH Sc = 50PF mutual inductance of 5 and the frequency of oscillations is 168 Hz.

2) In a transistorized Hartley oscillator the two inductance are 2mh and 20 while the frequency is to be changed from 950 KHZ to 2050 KHZ. Calculate the range over which the capacitor is to be varied.